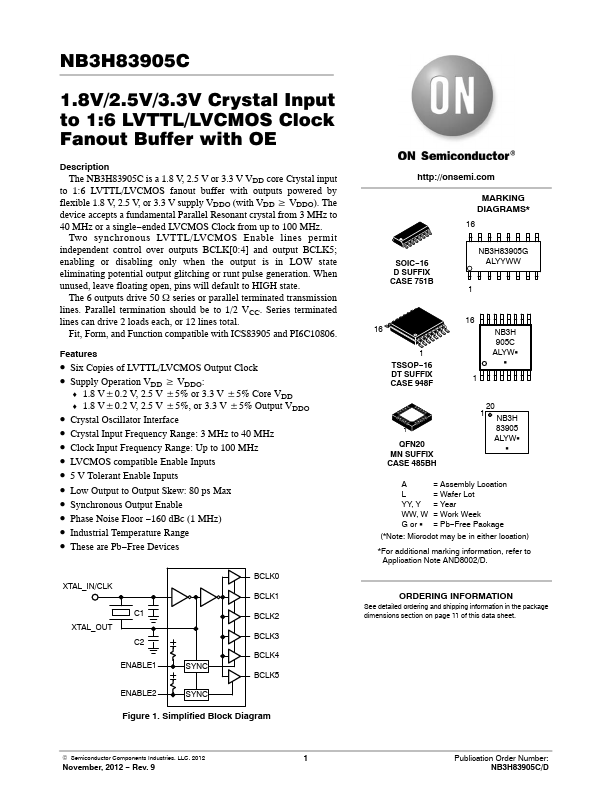

NB3H83905C Description

The NB3H83905C is a 1.8 V, 2.5 V or 3.3 V VDD core Crystal input to 1:6 LVTTL/LVCMOS fanout buffer with outputs powered by flexible 1.8 V, 2.5 V, or 3.3 V supply VDDO (with VDD w VDDO). The device accepts a fundamental Parallel Resonant crystal from 3 MHz to 40 MHz or a single−ended LVCMOS Clock from up to 100 MHz. Two synchronous LVTTL/LVCMOS Enable lines permit independent control over outputs BCLK[0:4] and output...

NB3H83905C Key Features

- Six Copies of LVTTL/LVCMOS Output Clock

- Supply Operation VDD w VDDO

- Crystal Oscillator Interface

- Crystal Input Frequency Range: 3 MHz to 40 MHz

- Clock Input Frequency Range: Up to 100 MHz

- LVCMOS patible Enable Inputs

- 5 V Tolerant Enable Inputs

- Low Output to Output Skew: 80 ps Max

- Synchronous Output Enable

- Phase Noise Floor -160 dBc (1 MHz)