NB3L553 Overview

Description

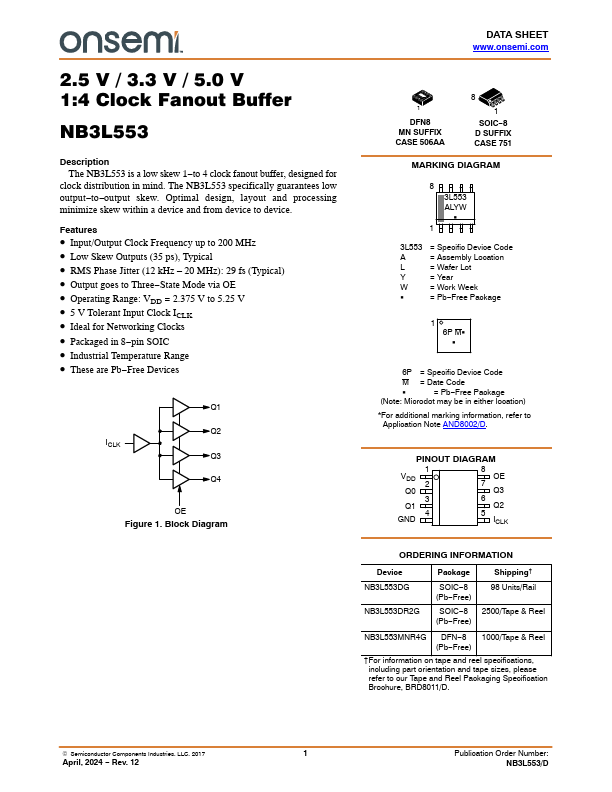

The NB3L553 is a low skew 1-to 4 clock fanout buffer, designed for clock distribution in mind. The NB3L553 specifically guarantees low output-to-output skew.

Key Features

- Input/Output Clock Frequency up to 200 MHz

- Low Skew Outputs (35 ps), Typical

- RMS Phase Jitter (12 kHz – 20 MHz): 29 fs (Typical)

- Output goes to Three-State Mode via OE

- Operating Range: VDD = 2.375 V to 5.25 V

- 5 V Tolerant Input Clock ICLK

- Ideal for Networking Clocks

- Packaged in 8-pin SOIC

- Industrial Temperature Range

- These are Pb-Free Devices Q1 Q2 ICLK Q3 Q4 OE Figure