NB3RL02 Description

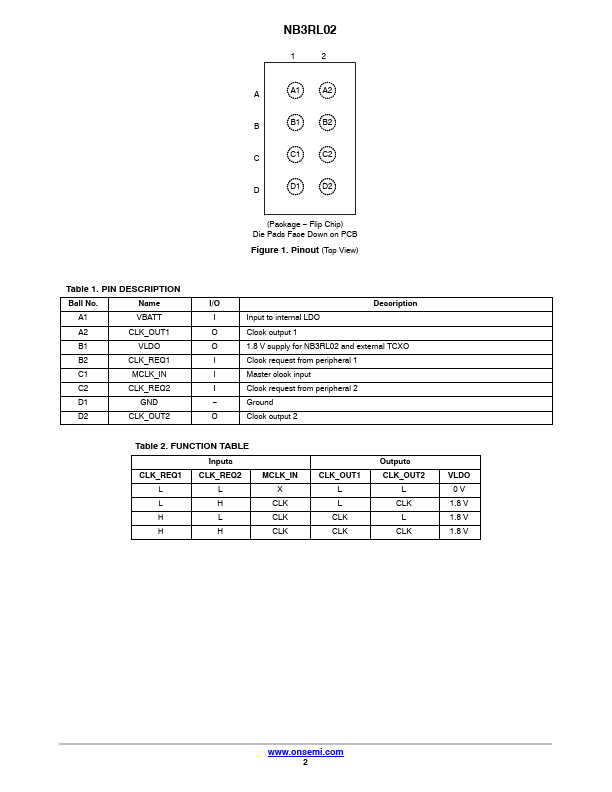

FUNCTION TABLE Inputs CLK_REQ1 CLK_REQ2 L L L H H L H H MCLK_IN X CLK CLK CLK CLK_OUT1 L L CLK CLK Outputs CLK_OUT2 L CLK L CLK VLDO 0V 1.8 V 1.8 V 1.8 V .onsemi. RATINGS Symbol Parameter Condition Min Max Unit VBATT.

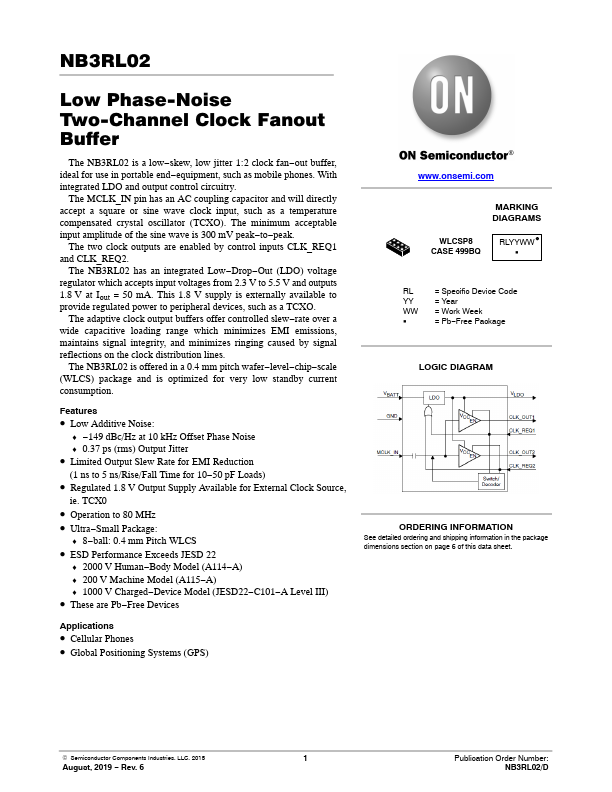

NB3RL02 Key Features

- Low Additive Noise

- 149 dBc/Hz at 10 kHz Offset Phase Noise

- 0.37 ps (rms) Output Jitter

- Limited Output Slew Rate for EMI Reduction

- Regulated 1.8 V Output Supply Available for External Clock Source

- Operation to 80 MHz

- Ultra-Small Package

- 8-ball: 0.4 mm Pitch WLCS

- ESD Performance Exceeds JESD 22

- 2000 V Human-Body Model (A114-A)