NB3W1200L Description

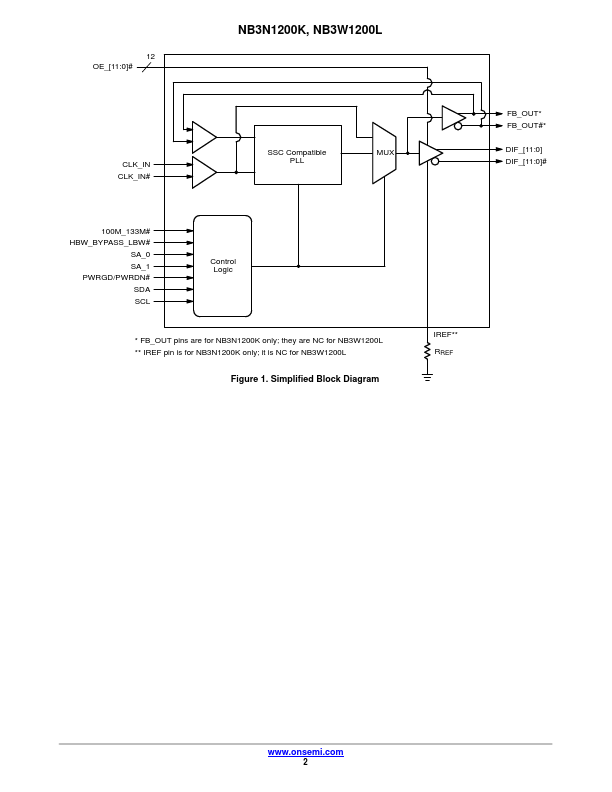

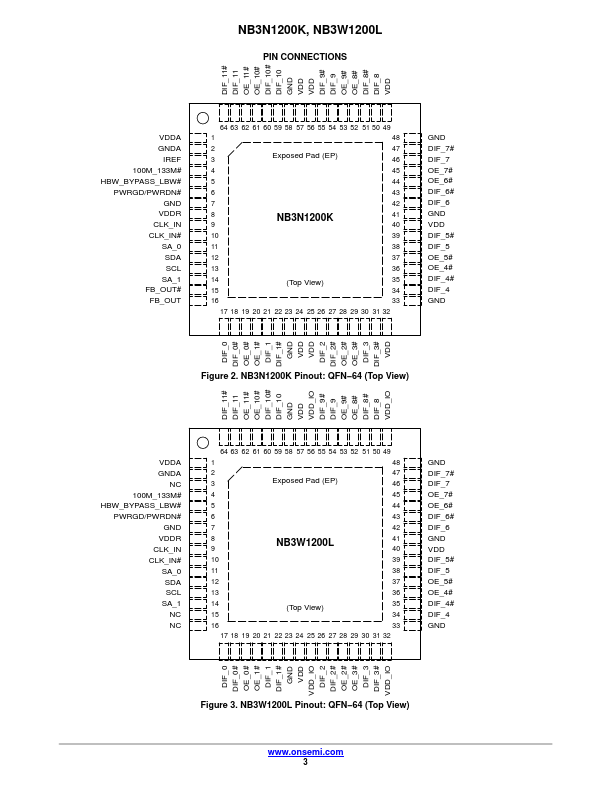

The NB3N1200K and NB3W1200L differential clock buffers are DB1200Z and DB1200ZL pliant and are designed to work in conjunction with a PCIe pliant source clock synthesizer to provide point−to−point clocks to multiple agents. The device is capable of distributing the reference clocks for Intel® QuickPath Interconnect (Intel QPI), PCIe Gen1/Gen2/Gen3, SAS, SATA, and Intel Scalable Memory Interconnect (Intel SMI)...

NB3W1200L Key Features

- 12 Differential Clock Output Pairs @ 0.7 V

- HCSL patible Outputs for NB3N