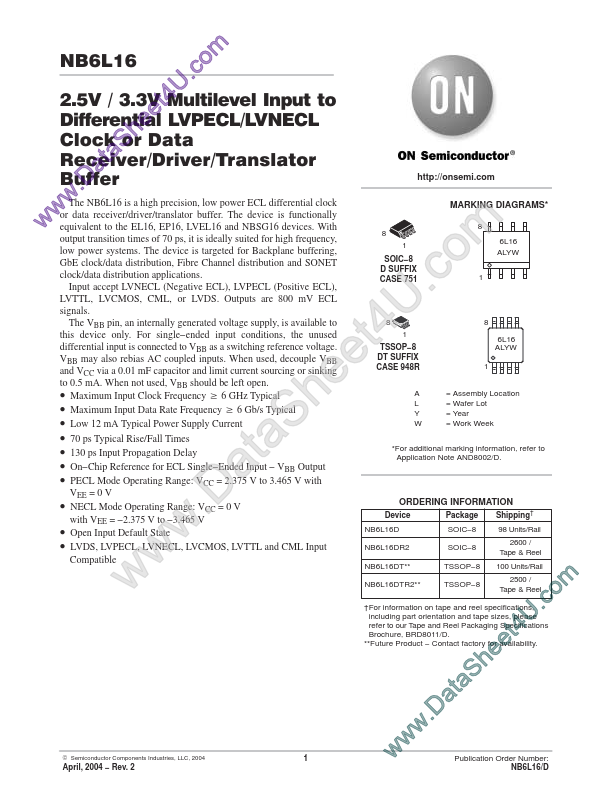

NB6L16 Description

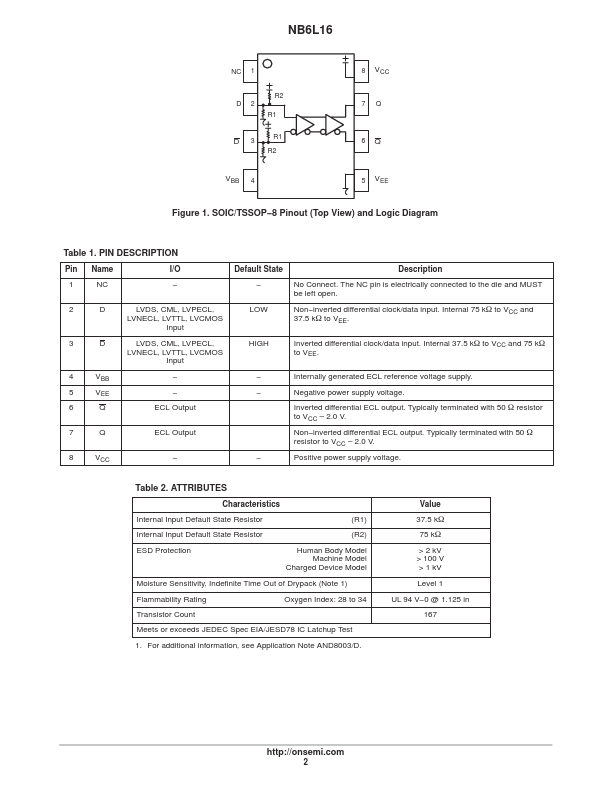

Pin 1 2 Name NC D I/O − LVDS, CML, LVPECL, LVNECL, LVTTL, LVCMOS Input LVDS, CML, LVPECL, LVNECL, LVTTL, LVCMOS Input − − ECL Output ECL Output − − Default State − LOW Description No Connect. The NC pin is electrically connected to the die and MUST be left open. Non−inverted differential clock/data input.