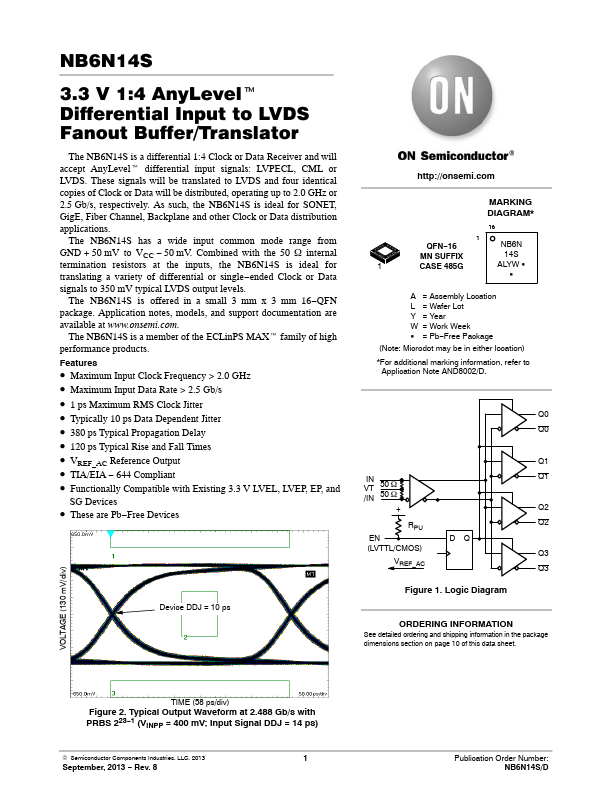

NB6N14S Overview

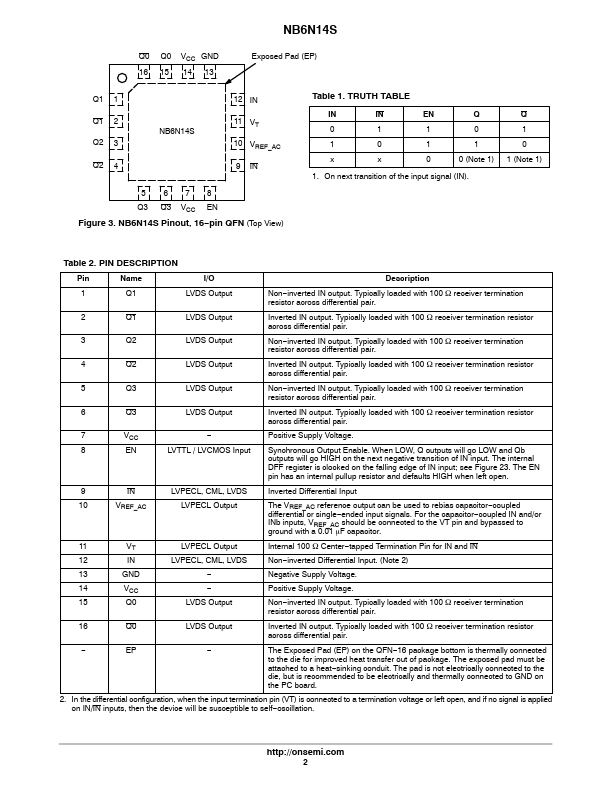

Pin Name I/O Description 1 Q1 LVDS Output Non−inverted IN output. Typically loaded with 100 W receiver termination resistor across differential pair. 2 Q1 LVDS Output Inverted IN output.

NB6N14S Key Features

- Maximum Input Clock Frequency > 2.0 GHz

- Maximum Input Data Rate > 2.5 Gb/s

- 1 ps Maximum RMS Clock Jitter

- Typically 10 ps Data Dependent Jitter

- 380 ps Typical Propagation Delay

- 120 ps Typical Rise and Fall Times

- VREF_AC Reference Output

- TIA/EIA

- 644 pliant

- Functionally patible with Existing 3.3 V LVEL, LVEP, EP, and