NV24C16MUW

NV24C16MUW is 16-Kb EEPROM manufactured by onsemi.

- Part of the NV24C02MUW comparator family.

- Part of the NV24C02MUW comparator family.

EEPROM Serial 2/4/8/16-Kb I2C Automotive Grade 1 in Wettable Flank UDFN-8

Package

NV24C02MUW, NV24C04MUW, NV24C08MUW, NV24C16MUW

Description The NV24C02/04/08/16 are EEPROM Serial 2/4/8/16- Kb I2C

Automotive Grade 1 devices organized internally as 16/32/64 and 128 pages respectively of 16 bytes each. All devices support the Standard (100 k Hz) and Fast (400 k Hz) I2C protocol.

Data is written by providing a starting address, then loading 1 to 16 contiguous bytes into a Page Write Buffer, and then writing all data to non- volatile memory in one internal write cycle. Data is read by providing a starting address and then shifting out data serially while automatically incrementing the internal address count.

External address pins make it possible to address up to eight NV24C02, four NV24C04, two NV24C08 and one NV24C16 device on the same bus.

Features

- Automotive AEC- Q100 Grade 1 (- 40°C to +125°C) Qualified

- Supports Standard, Fast and Fast- Plus I2C Protocol

- 2.5 V to 5.5 V Supply Voltage Range

- 16- Byte Page Write Buffer

- Fast Write Time (4 ms max)

- Hardware Write Protection for Entire Memory

- Schmitt Triggers and Noise Suppression Filters on I2C Bus Inputs

(SCL and SDA)

- Low power CMOS Technology

- More than 1,000,000 Program/Erase Cycles

- 100 Year Data Retention

- UDFN- 8 (2 x 3 mm) Wettable Flank Package (- 40°C to +125°C)

- These Devices are Pb- Free, Halogen Free/BFR Free and are Ro HS pliant

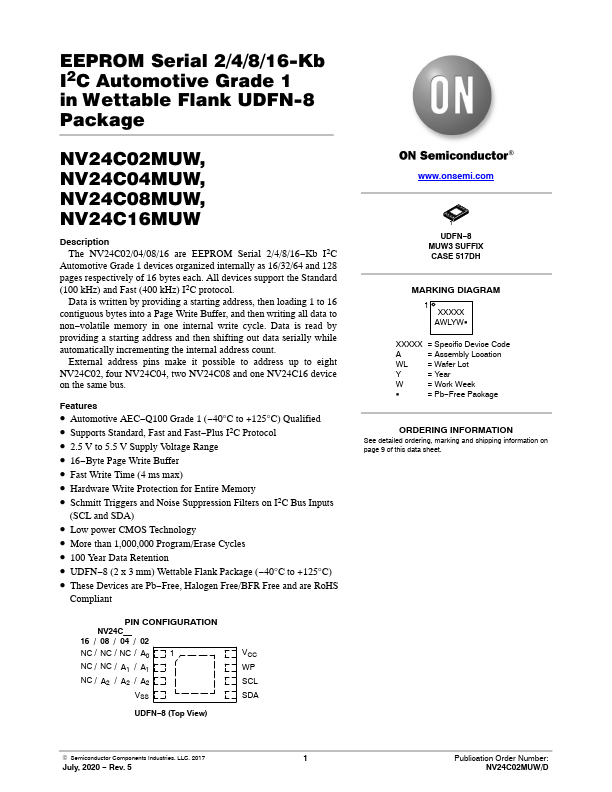

PIN CONFIGURATION

NV24C__

16 / 08 / 04 / 02

NC / NC / NC / A0

NC / NC / A1 / A1 NC / A2 / A2 / A2

UDFN- 8 (Top View)

VCC WP SCL SDA

.onsemi.

UDFN- 8 MUW3 SUFFIX CASE...