PM4325

PM4325 is Octal Short Haul T1/E1/J1 Low Latency Transport Line Interface manufactured by PMC-Sierra.

- Part of the PM4325_PMC comparator family.

- Part of the PM4325_PMC comparator family.

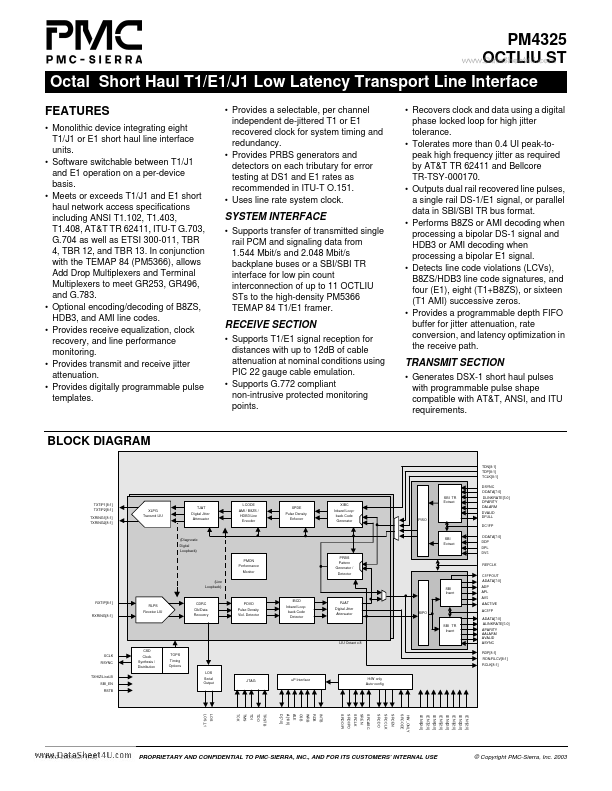

PM4325 .. OCTLIU ST Octal Short Haul T1/E1/J1 Low Latency Transport Line Interface

Features

- Monolithic device integrating eight T1/J1 or E1 short haul line interface units.

- Software switchable between T1/J1 and E1 operation on a per-device basis.

- Meets or exceeds T1/J1 and E1 short haul network access specifications including ANSI T1.102, T1.403, T1.408, AT&T TR 62411, ITU-T G.703, G.704 as well as ETSI 300-011, TBR 4, TBR 12, and TBR 13. In conjunction with the TEMAP 84 (PM5366), allows Add Drop Multiplexers and Terminal Multiplexers to meet GR253, GR496, and G.783.

- Optional encoding/decoding of B8ZS, HDB3, and AMI line codes.

- Provides receive equalization, clock recovery, and line performance monitoring.

- Provides transmit and receive jitter attenuation.

- Provides digitally programmable pulse templates.

- Provides a selectable, per channel independent de-jittered T1 or E1 recovered clock for system timing and redundancy.

- Provides PRBS generators and detectors on each tributary for error testing at DS1 and E1 rates as remended in ITU-T O.151.

- Uses line rate system clock.

- Recovers clock and data using a digital phase locked loop for high jitter tolerance.

- Tolerates more than 0.4 UI peak-topeak high frequency jitter as required by AT&T TR 62411 and Bellcore TR-TSY-000170.

- Outputs dual rail recovered line pulses, a single rail DS-1/E1 signal, or parallel data in SBI/SBI TR bus format.

- Performs B8ZS or AMI decoding when processing a bipolar DS-1 signal and HDB3 or AMI decoding when processing a bipolar E1 signal.

- Detects line code violations (LCVs), B8ZS/HDB3 line code signatures, and four (E1), eight (T1+B8ZS), or sixteen (T1 AMI) successive zeros.

- Provides a programmable depth FIFO buffer for jitter attenuation, rate conversion, and latency optimization in the receive path.

SYSTEM INTERFACE

- Supports transfer of transmitted single rail PCM and signaling data from 1.544 Mbit/s and 2.048 Mbit/s backplane buses or a...