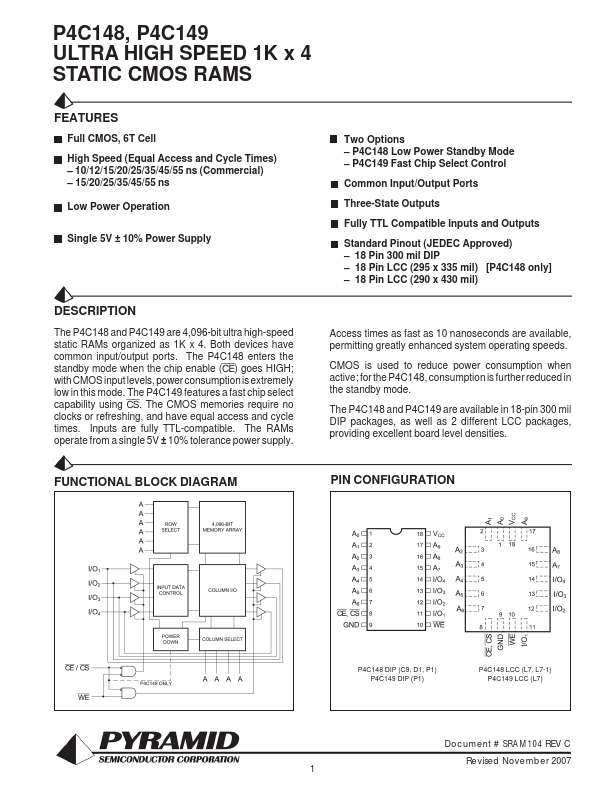

P4C149 Description

The P4C148 and P4C149 are 4,096-bit ultra high-speed static RAMs organized as 1K x 4. Both devices have mon input/output ports. The P4C148 enters the standby mode when the chip enable (CE) goes HIGH;.

P4C149 Key Features

- 10/12/15/20/25/35/45/55 ns (mercial)

- 15/20/25/35/45/55 ns

- P4C148 Low Power Standby Mode

- P4C149 Fast Chip Select Control

- 18 Pin 300 m