PJDLC15 Description

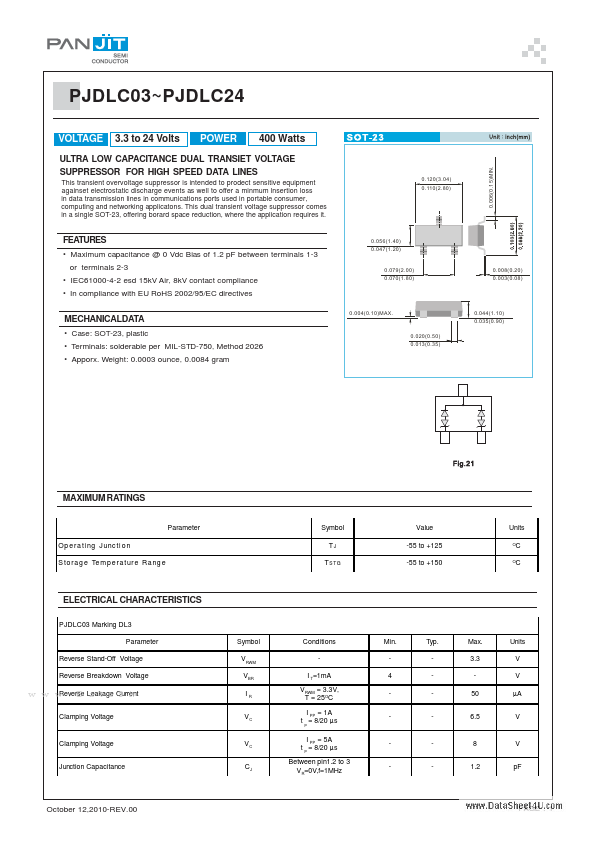

PJDLC03~PJDLC24 VOLTAGE 3.3 to 24 Volts POWER 400 Watts 0.006(0.15)MIN. This dual transient voltage suppressor es in a single SOT-23, offering borard space reduction, where the application requires it.

PJDLC15 Key Features

- Maximum capacitance @ 0 Vdc Bias of 1.2 pF between terminals 1-3 or terminals 2-3

- IEC61000-4-2 esd 15kV Air, 8kV contact pliance

- In pliance with EU RoHS 2002/95/EC directives

- Case: SOT-23, plastic

- Terminals: solderable per MIL-STD-750, Method 2026

- Apporx. Weight: 0.0003 ounce, 0.0084 gram