Datasheet Summary

For munications Equipment

Single-Chip Fax Engine LSI

Overview

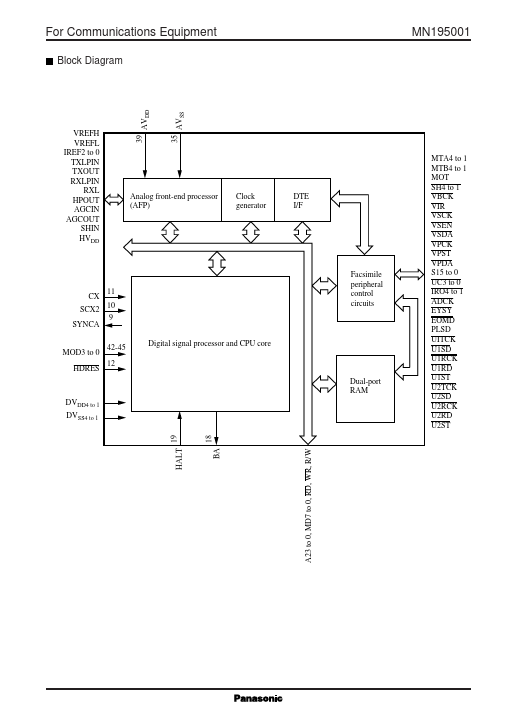

The MN195001 reduces to a single chip CPU functions related to facsimile control, peripheral device control functions, and modem functions. The last include plete fax/modem support for the ITU-T G3 remandations V.29, V.27ter, and V.21 Channels 1 and 2. The MN195001 consists of the following blocks: digital signal processor (DSP), facsimile peripheral circuits, analog circuits, DTE interface, clock generator, and dualport RAM. Changing the contents of an external ROM tailors the chip for a wide variety of facsimile applications.

Features

Digital signal processor (DSP) block

- Micro ROM: 4096 × 32 bits

- Data...