PI6CDBL402B Description

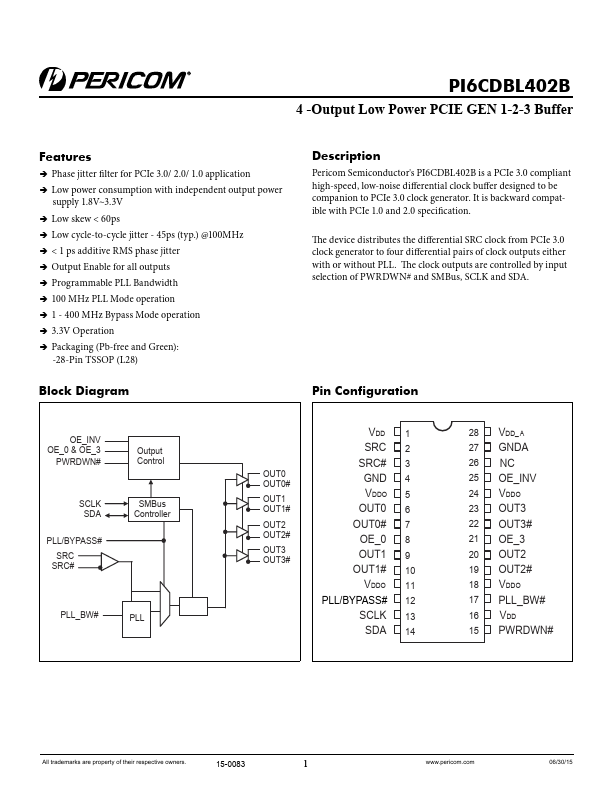

Peri Semiconductor's PI6CDBL402B is a PCIe 3.0 pliant high-speed, low-noise differential clock buffer designed to be panion to PCIe 3.0 clock generator. It is backward patible with PCIe 1.0 and 2.0 specification. The device distributes the differential SRC clock from PCIe 3.0 clock generator to four differential pairs of clock outputs either with or without PLL.

PI6CDBL402B Key Features

- 45ps (typ.) @100MHz ÎÎ< 1 ps additive RMS phase jitter ÎÎOutput Enable for all outputs ÎÎProgrammable PLL Bandwidth ÎÎ10

- 400 MHz Bypass Mode operation ÎÎ3.3V Operation ÎÎPackaging (Pb-free and Green)

- 28-Pin TSSOP (L28)