PM49FL002T-33VC

Overview

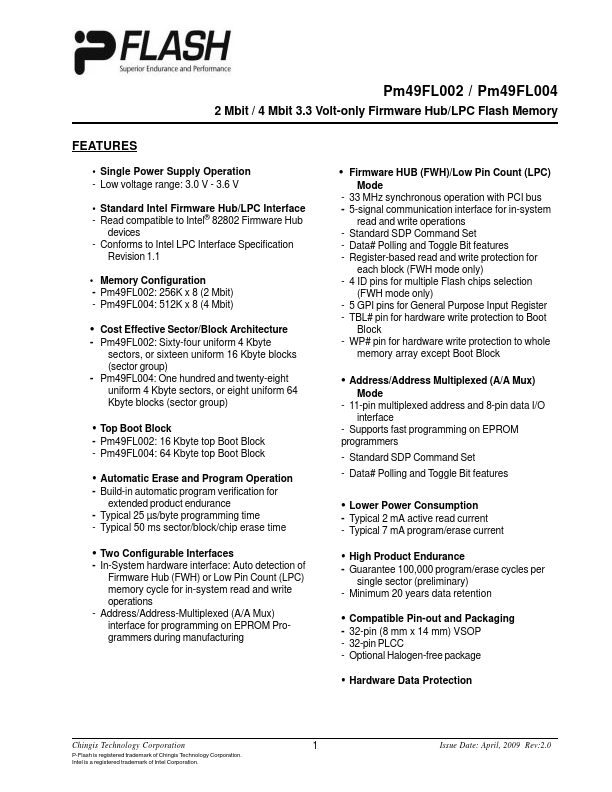

- Single Power Supply Operation - Low voltage range: 3.0 V - 3.6 V

- Standard Intel Firmware Hub/LPC Interface - Read compatible to Intel® 82802 Firmware Hub devices - Conforms to Intel LPC Interface Specification Revision 1.1

- Memory Configuration - Pm49FL002: 256K x 8 (2 Mbit) - Pm49FL004: 512K x 8 (4 Mbit)

- Cost Effective Sector/Block Architecture - Pm49FL002: Sixty-four uniform 4 Kbyte sectors, or sixteen uniform 16 Kbyte blocks (sector group) - Pm49FL004: One hundred and twenty-eight uniform 4 Kbyte sectors, or eight uniform 64 Kbyte blocks (sector group)

- Top Boot Block - Pm49FL002: 16 Kbyte top Boot Block - Pm49FL004: 64 Kbyte top Boot Block

- Automatic Erase and Program Operation - Build-in automatic program verification for extended product endurance - Typical 25 µs/byte programming time - Typical 50 ms sector/block/chip erase time

- Two Configurable Interfaces - In-System hardware interface: Auto detection of Firmware Hub (FWH) or Low Pin Count (LPC) memory cycle for in-system read and write operations - Address/Address-Multiplexed (A/A Mux) interface for programming on EPROM Programmers during manufacturing

- Firmware HUB (FWH)/Low Pin Count (LPC) Mode - 33 MHz synchronous operation with PCI bus - 5-signal communication interface for in-system read and write operations - Standard SDP Command Set - Data# Polling and Toggle Bit features - Register-based read and write protection for each block (FWH mode only) - 4 ID pins for multiple Flash chips selection (FWH mode only) - 5 GPI pins for General Purpose Input Register - TBL# pin for hardware write protection to Boot Block - WP# pin for hardware write protection to whole memory array except Boot Block

- Address/Address Multiplexed (A/A Mux) Mode - 11-pin multiplexed address and 8-pin data I/O interface - Supports fast programming on EPROM programmers - Standard SDP Command Set - Data# Polling a