PCS3P623Z05A Description

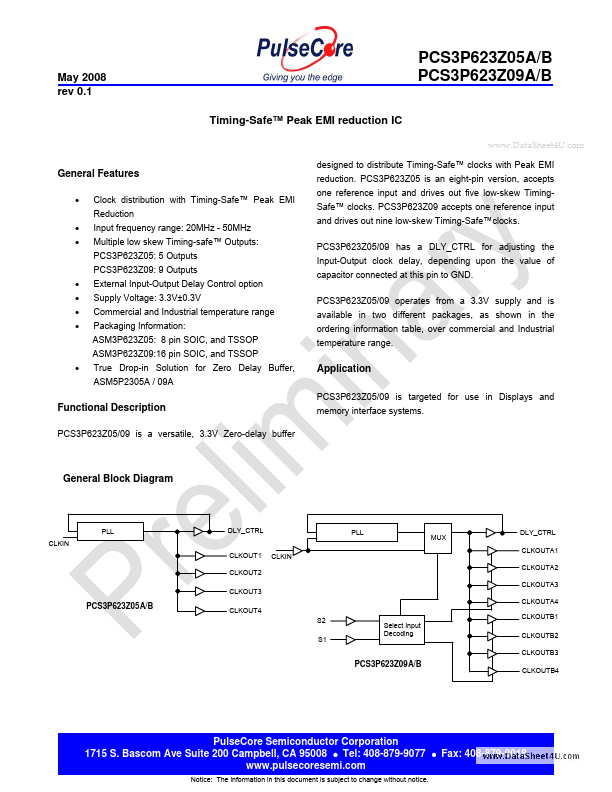

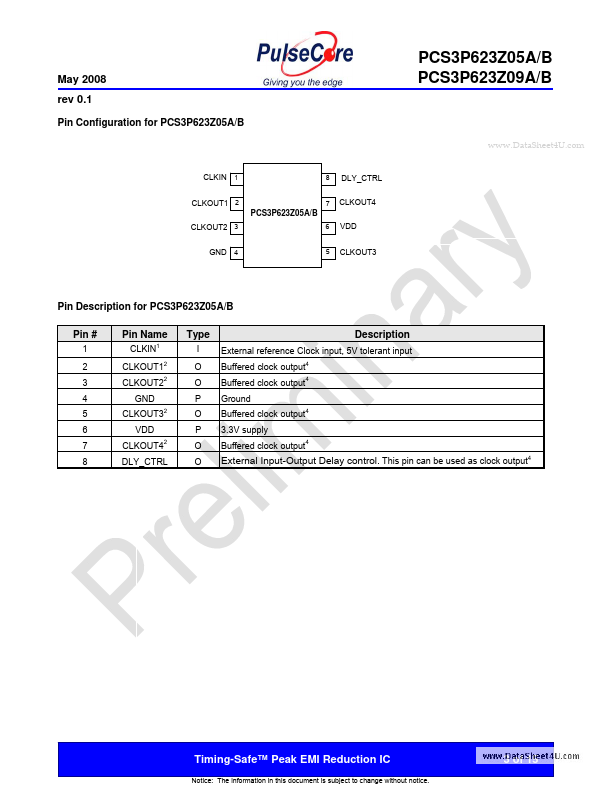

PCS3P623Z05/09 is a versatile, 3.3V Zero-delay buffer memory interface systems. Bas Ave Suite 200 Campbell, CA 95008 Tel: 408-879-9018 .pulsecoresemi.

PCS3P623Z05A Key Features

- Clock distribution with Timing-Safe™ Peak EMI Reduction Input frequency range: 20MHz

- True Drop-in Solution for Zero Delay Buffer, ASM5P2305A / 09A

- Tel: 408-879-9077

- Fax: 408-879-9018 .pulsecoresemi