HYS72T64301HP-3.7-A Description

HYS72T64301HP [3S/3.7] A 240-Pin Registered DDR2 SDRAM Modules DDR2 SDRAM RDIMM SDRAM RoHs pliant Internet Data Sheet Rev. 1.0 Internet Data Sheet .. HYS72T64301HP [3S/3.7] A Registered DDR2 SDRAM Modules HYS72T64301HP [3S/3.7] A Revision History:.

HYS72T64301HP-3.7-A Key Features

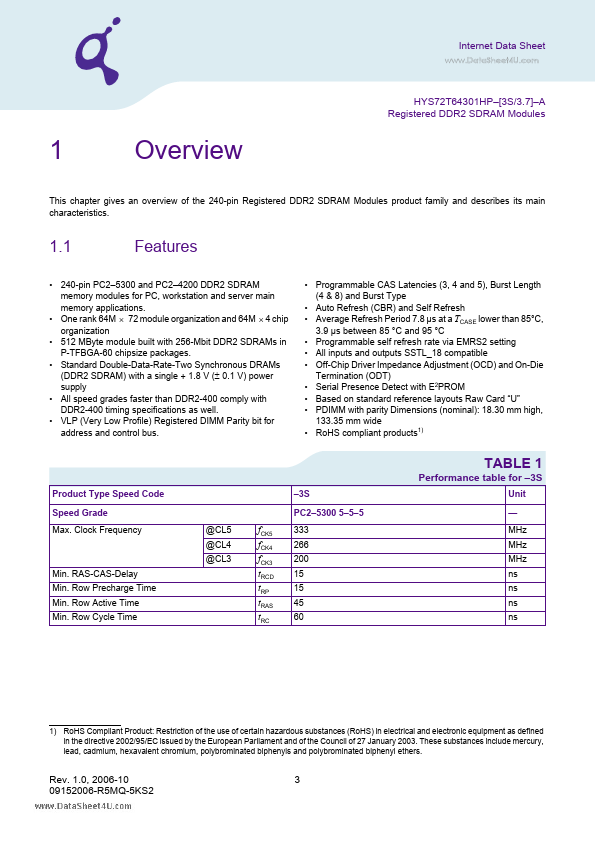

- Programmable CAS Latencies (3, 4 and 5), Burst Length (4 & 8) and Burst Type

- Auto Refresh (CBR) and Self Refresh

- Average Refresh Period 7.8 µs at a TCASE lower than 85°C, 3.9 µs between 85 °C and 95 °C

- Programmable self refresh rate via EMRS2 setting

- All inputs and outputs SSTL_18 patible

- Off-Chip Driver Impedance Adjustment (OCD) and On-Die Termination (ODT)

- Serial Presence Detect with E2PROM

- Based on standard reference layouts Raw Card “U”

- PDIMM with parity Dimensions (nominal): 18.30 mm high, 133.35 mm wide

- RoHS pliant products1)