CH5321

Overview

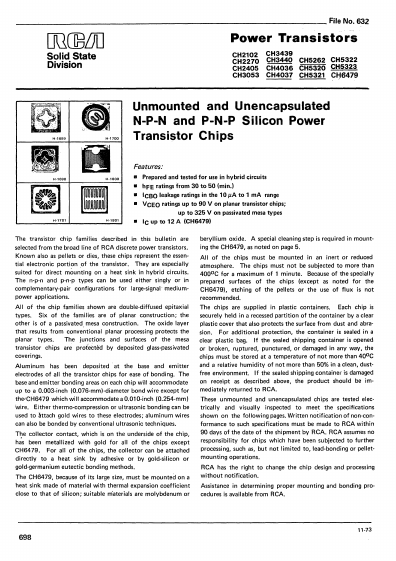

- Prepared and tested for use in hybrid qircuits

- hFE ratings from 30 to 50 (min.)

- ICBO leakage ratings in the 10 IlA to 1 mA range

- VCEO ratings up to 90 V on planar transistor chips; up to 325 V on passivated mesa ty pes H-1B01

- IC up to 12 A (CH6479) The transistor chip families described in this bulletin are selected from the broad line of RCA discrete power transistors. Known also as pellets or dies. these chips represent the essen

- tial electronic portion of the transistor. They are especially suited for direct mou~ting on a heat sink in hybrid circuits. The n

- n and p

- p types can be used either singly or in complementary

- pair configurations fo