BU90T82

BU90T82 is 27bit LVDS Dual-out Transmitter manufactured by ROHM.

Description

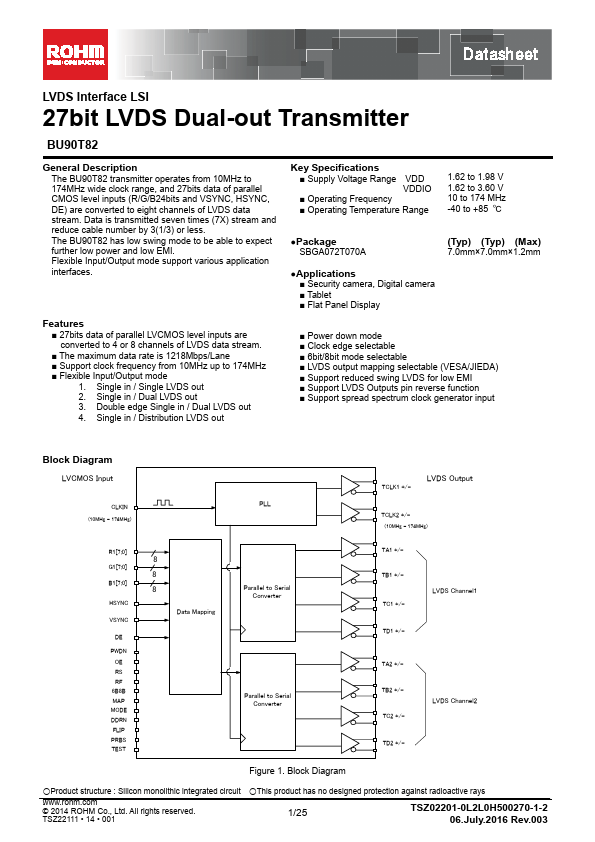

The BU90T82 transmitter operates from 10MHz to 174MHz wide clock range, and 27bits data of parallel CMOS level inputs (R/G/B24bits and VSYNC, HSYNC, DE) are converted to eight channels of LVDS data stream. Data is transmitted seven times (7X) stream and reduce cable number by 3(1/3) or less. The BU90T82 has low swing mode to be able to expect further low power and low EMI. Flexible Input/Output mode support various application interfaces.

Features

- 27bits data of parallel LVCMOS level inputs are converted to 4 or 8 channels of LVDS data stream.

- The maximum data rate is 1218Mbps/Lane

- Support clock frequency from 10MHz up to 174MHz

- Flexible Input/Output mode

1. Single in / Single LVDS out 2. Single in / Dual LVDS out 3. Double edge Single in / Dual LVDS out 4. Single in / Distribution LVDS out

Key Specifications

- Supply Voltage Range VDD VDDIO

- Operating Frequency

-...