621S

621S is Low Skew 1 to 4 Clock Buffer manufactured by Renesas.

Low Skew 1 to 4 Clock Buffer

Description

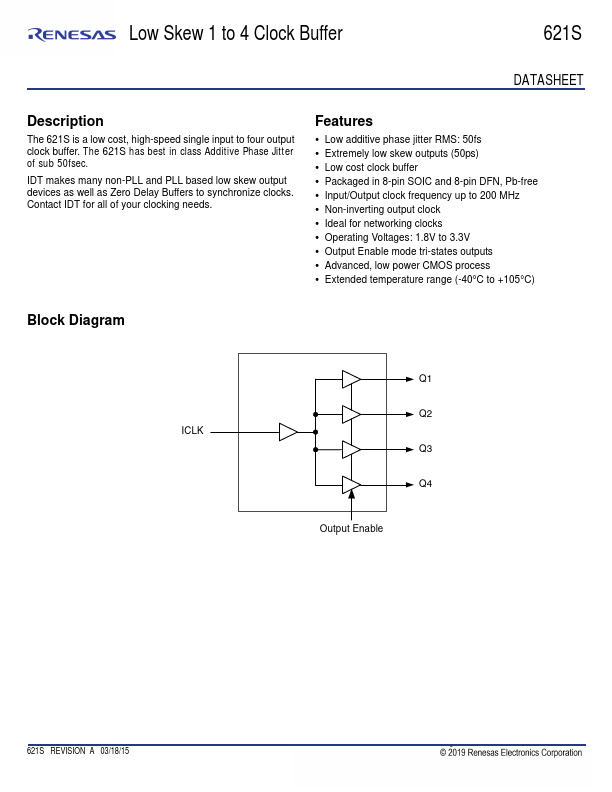

The 621S is a low cost, high-speed single input to four output clock buffer. The 621S has best in class Additive Phase Jitter of sub 50fsec.

IDT makes many non-PLL and PLL based low skew output devices as well as Zero Delay Buffers to synchronize clocks. Contact IDT for all of your clocking needs.

Features

- Low additive phase jitter RMS: 50fs

- Extremely low skew outputs (50ps)

- Low cost clock buffer

- Packaged in 8-pin SOIC and 8-pin DFN, Pb-free

- Input/Output clock frequency up to 200 MHz

- Non-inverting output clock

- Ideal for networking clocks

- Operating Voltages: 1.8V to 3.3V

- Output Enable mode tri-states outputs

-...