650R-27ILF Overview

Key Specifications

Package: QSOP

Mount Type: Surface Mount

Pins: 20

Operating Voltage: 3.3 V

Description

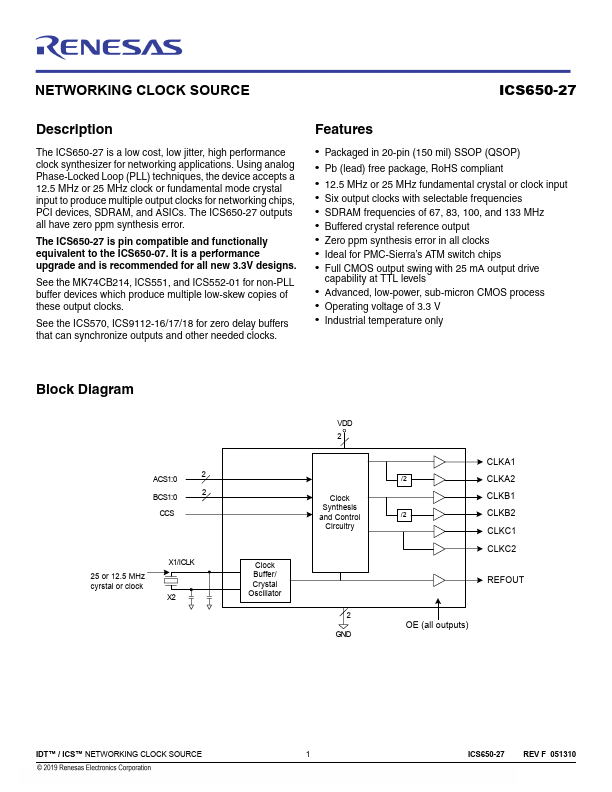

The ICS650-27 is a low cost, low jitter, high performance clock synthesizer for networking applications. Using analog Phase-Locked Loop (PLL) techniques, the device accepts a 12.5 MHz or 25 MHz clock or fundamental mode crystal input to produce multiple output clocks for networking chips, PCI devices, SDRAM, and ASICs.

Key Features

- Packaged in 20-pin (150 mil) SSOP (QSOP)

- Pb (lead) free package, RoHS compliant

- 12.5 MHz or 25 MHz fundamental crystal or clock input

- Six output clocks with selectable frequencies

- SDRAM frequencies of 67, 83, 100, and 133 MHz

- Buffered crystal reference output

- Zero ppm synthesis error in all clocks

- Ideal for PMC-Sierra’s ATM switch chips

- Full CMOS output swing with 25 mA output drive capability at TTL levels

- Advanced, low-power, sub-micron CMOS process