7006S Overview

Key Specifications

Mount Type: Screw

Length: 11.1125 mm

Description

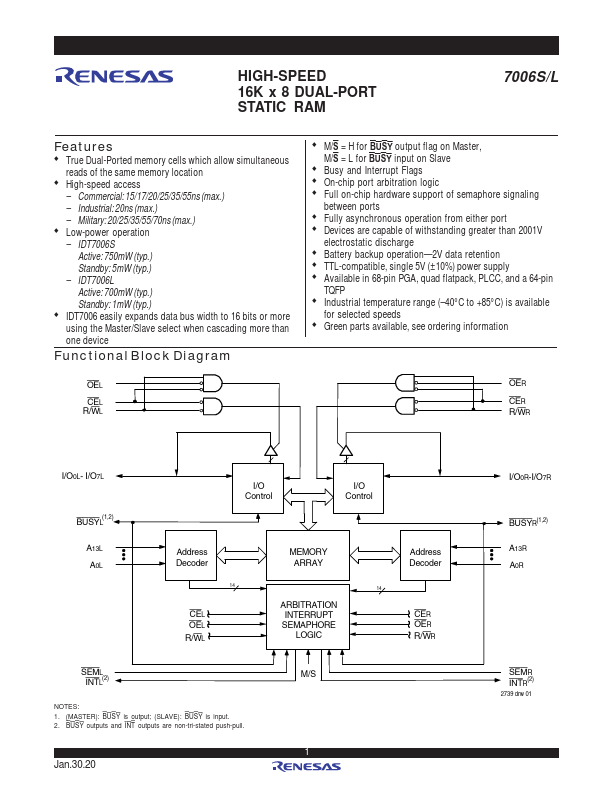

The IDT7006 is a high-speed 16K x 8 Dual-Port Static RAM. The IDT7006 is designed to be used as a stand-alone 128K-bit Dual-Port RAM or as a combination MASTER/SLAVE Dual-Port RAM for 16-bit-or-more word systems.

Key Features

- True Dual-Ported memory cells which allow simultaneous reads of the same memory location

- Low-power operation – IDT7006S Active: 750mW (typ.) Standby: 5mW (typ.) – IDT7006L Active: 700mW (typ.) Standby: 1mW (typ.)

- IDT7006 easily expands data bus width to 16 bits or more using the Master/Slave select when cascading more than one device