8P791208

8P791208 is Low Additive Jitter 2:8 Buffer manufactured by Renesas.

Low Additive Jitter 2:8 Buffer with CMOS / Differential Outputs

8P791208 Datasheet

Description

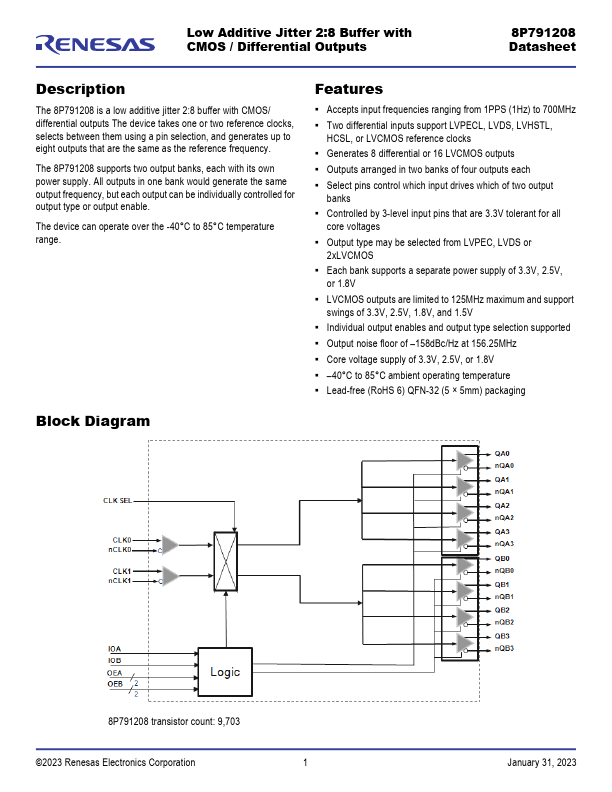

The 8P791208 is a low additive jitter 2:8 buffer with CMOS/ differential outputs The device takes one or two reference clocks, selects between them using a pin selection, and generates up to eight outputs that are the same as the reference frequency.

The 8P791208 supports two output banks, each with its own power supply. All outputs in one bank would generate the same output frequency, but each output can be individually controlled for output type or output enable.

The device can operate over the -40°C to 85°C temperature range.

Features

- Accepts input frequencies ranging from 1PPS (1Hz) to...