8T74S208A-01

8T74S208A-01 is LVDS Clock Divider and Fanout Buffer manufactured by Renesas.

2.5V Differential LVDS Clock Divider and Fanout Buffer

REFER TO PCN# N1608-01, Effective Date November 18, 2016 FOR NEW DESIGNS USE PART NUMBER 8T74S208C-01

DATA SHEET

General Description

The 8T74S208A-01 is a high-performance differential LVDS clock divider and fanout buffer. The device is designed for the frequency division and signal fanout of high-frequency, low phase-noise clocks. The 8T74S208A-01 is characterized to operate from a 2.5V power supply. Guaranteed output-to-output and part-to-part skew characteristics make the 8T74S208A-01 ideal for those clock distribution applications demanding well-defined performance and repeatability. The integrated input termination resistors make interfacing to the reference source easy and reduce passive ponent count. Each output can be individually enabled or disabled in the high-impedance state controlled by a I2C register. On power-up, all outputs are disabled.

Features

One differential input reference clock Differential pair can accept the following differential input levels: LVDS, LVPECL, CML Integrated input termination resistors Eight LVDS outputs Selectable clock frequency division of ÷1, ÷2, ÷4 and ÷8 Maximum input clock frequency: 1GHz LVCMOS interface levels for the control inputs Individual output enabled/ disabled by I2C interface Output skew: 45ps (maximum) Output rise/fall times: 370ps (maximum) Low additive phase jitter, RMS: 96fs (typical) Full 2.5V supply voltage Outputs disable at power up Lead-free (Ro HS 6) 32-Lead VFQFN packaging -40°C to 85°C ambient operating temperature

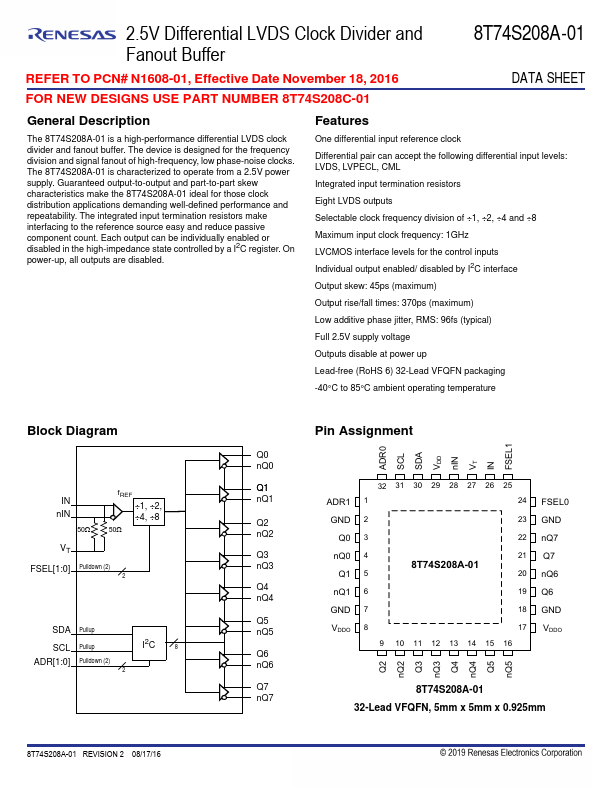

Block Diagram

IN n IN

50 f REF

÷1, ÷2, ÷4, ÷8

50

VT FSEL[1:0] Pulldown (2)

SDA Pullup

SCL Pullup ADR[1:0] Pulldown (2)

I2C

Pin Assignment

ADR0 SCL SDA VDD n IN VT IN FSEL1

Q0 n Q0

Q1 n Q1

Q2 n Q2

Q3 n Q3

Q4 n Q4

Q5 n Q5

Q6 n Q6

ADR1 GND

Q0 n Q0

Q1 n Q1 GND VDDO

32 31 30 29 28 27 26 25 1 24

2...