9DBV0841

Overview

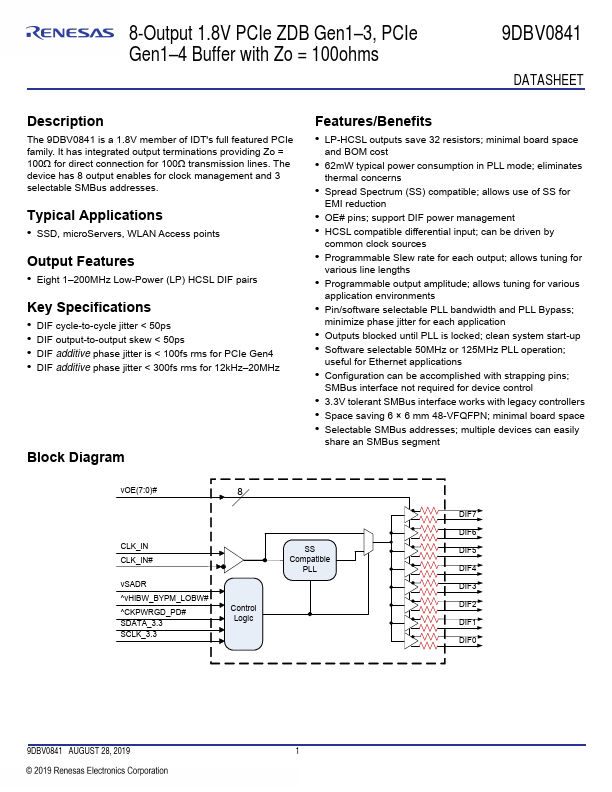

The 9DBV0841 is a 1.8V member of IDT's full featured PCIe family. It has integrated output terminations providing Zo = 100 for direct connection for 100 transmission lines.

- Eight 1-200MHz Low-Power (LP) HCSL DIF pairs Key Specifications

- DIF cycle-to-cycle jitter < 50ps

- DIF output-to-output skew < 50ps

- DIF additive phase jitter is < 100fs rms for PCIe Gen4

- DIF additive phase jitter < 300fs rms for 12kHz-20MHz