9INT31H200 Overview

Description

The 9INT31H200 is a 2-output very high-performance HCSL fanout buffer for high performance interconnect applications. It can be used at speeds up to 350MHz and is compliant to the DB200H specification.

Key Features

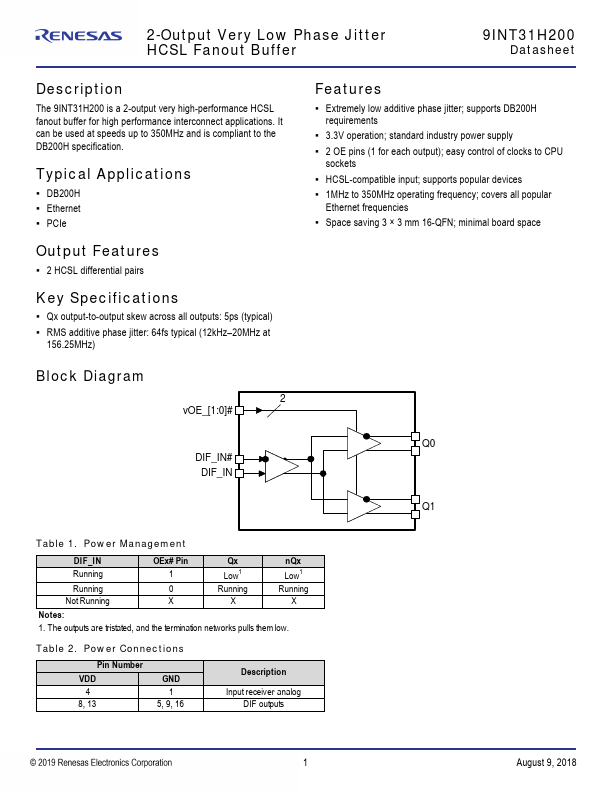

- Power Management DI F_I N OEx# Pin Qx nQx Running 1 Low1 Low1 Running 0 Running Running Not Running X X X Notes

- The outputs are tristated, and the termination networks pulls them low. Table

- Power Connections Pin Number VDD GND 41 8, 13 5, 9, 16