9Z61195D

9Z61195D is 19-Output DB1900Z Derivative manufactured by Renesas.

Description

The 9Z61195D is a second-generation, enhanced-performance DB1900Z derivative differential buffer. The part is a pin-patible upgrade to the 9Z61195A, offering much improved phase jitter performance. A fixed external feedback maintains low drift for critical QPI/UPI applications. In fanout mode, the 9Z61195D meets the DB2000Q additive phase jitter specification.

PCIe Clocking Architectures

- mon Clocked (CC)

- Independent Reference (IR) with and without spread spectrum

Typical Applications

- Servers

- Storage

- Networking

- SSDs

Output Features

- 19 Low-Power (LP) HCSL output pairs with 85Ω Zout

Features

- LP-HCSL outputs with 85Ω Zout; eliminate 76 resistors, save 130mm2 of area

- SMBus OE bits; software control of each output

- 9 selectable SMBus addresses; multiple devices can share same SMBus segment

- Selectable PLL bandwidths; minimizes jitter peaking in cascaded PLL topologies

- Hardware/SMBus control of PLL bandwidth and bypass; change mode without power cycle

- Spread spectrum patible; tracks spreading input clock for

EMI reduction

- 10 × 10 mm 72-VFQFPN package; small board footprint

Key Specifications

- Cycle-to-cycle jitter: < 50ps

- Output-to-output skew: < 50ps

- Input-to-output delay: Fixed at 0ps

- Input-to-output delay variation: < 50ps

- Additive Phase jitter: PCIe Gen4 < 53fs rms

- Additive Phase jitter: IF-UPI < 70fs rms

- Additive Phase jitter: DB2000Q filter < 30fs rms

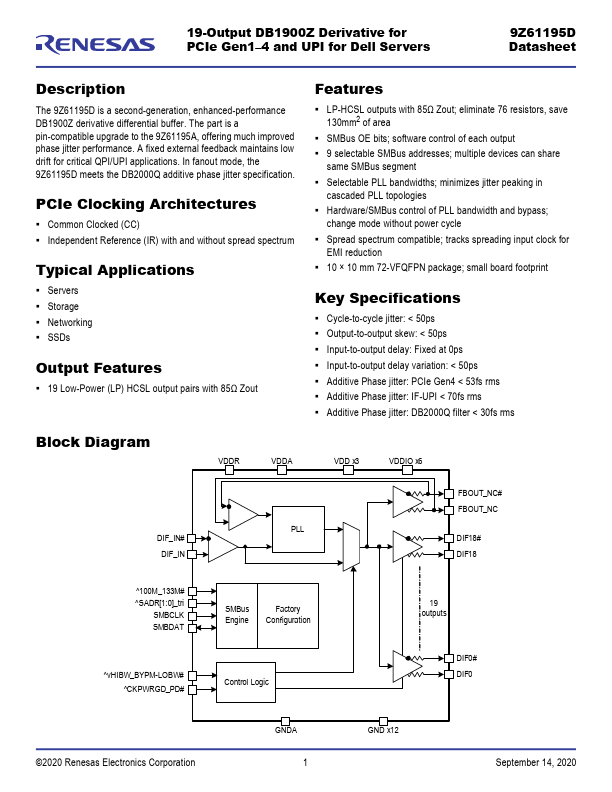

Block Diagram

VDDR

VDDA

VDD x3

VDDIO x6

PLL DIF_IN# DIF_IN

FBOUT_NC# FBOUT_NC

DIF18# DIF18

^100M_133M# ^SADR[1:0]_tri

SMBCLK...