9ZML1255

9ZML1255 is 2:12 Clock Multiplexer manufactured by Renesas.

- Part of the 9ZML1245 comparator family.

- Part of the 9ZML1245 comparator family.

2:12 Clock Multiplexer for PCIe Gen1- 5 and UPI

9ZML1245/9ZML1255/ 9ZML1256

Description

The 9ZML1245/9ZML1255/9ZML1256 devices are third generation enhanced performance 2-input, 12-output clock multiplexers. Each input clock has software adjustable input-to-output delay when operating in Zero-Delay (ZDB) mode. The devices also implement an extensive set of Features ensuring that clocks are well behaved with today's ever more plex power-up sequencing. The 9ZML1256 has an SMBus Write Lockout pin for increased device and system security.

PCIe Clocking Architectures

- mon Clocked (CC)

- Independent Reference (IR) with and without spread spectrum

Key Specifications

- Fanout Buffer Mode additive phase jitter:

- PCIe Gen5 CC < 15fs RMS

- DB2000Q additive jitter < 25fs RMS

- QPI/UPI 11.4GB/s < 40fs RMS

- IF-UPI additive jitter < 70fs RMS

- ZDB Mode phase jitter:

- PCIe Gen5 CC < 24fs RMS

- QPI/UPI 11.4GB/s < 110fs RMS

- IF-UPI additive jitter < 130fs RMS

- Cycle-to-cycle jitter < 50ps

- Output-to-output skew < 50ps

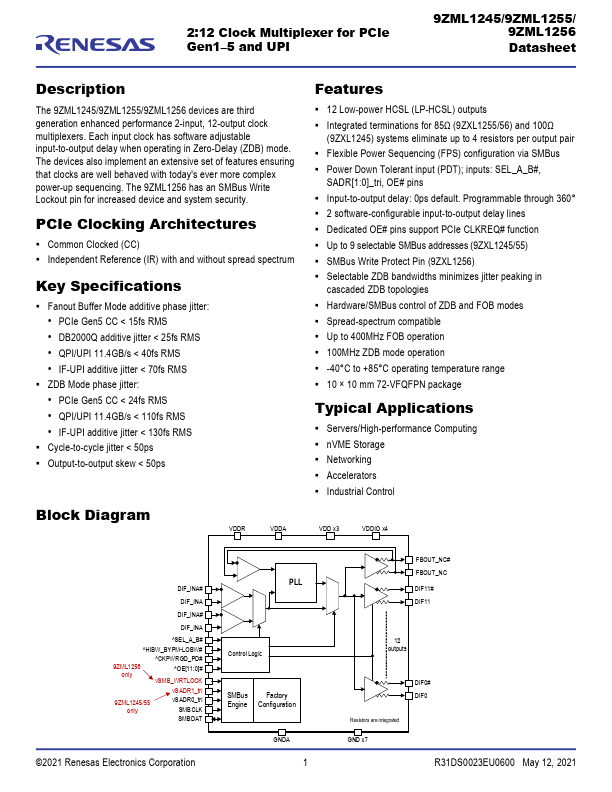

Block Diagram

VDDR

VDDA

Features

- 12 Low-power HCSL (LP-HCSL) outputs

- Integrated terminations for 85Ω (9ZXL1255/56) and 100Ω

(9ZXL1245) systems eliminate up to 4 resistors per output pair

- Flexible Power Sequencing (FPS) configuration via SMBus

- Power Down Tolerant input (PDT); inputs: SEL_A_B#,

SADR[1:0]_tri, OE# pins

- Input-to-output delay: 0ps default. Programmable through...