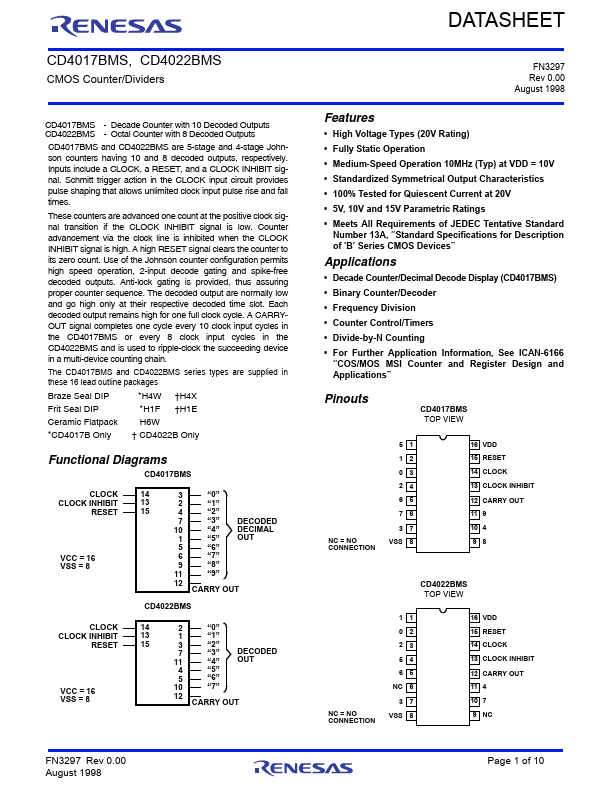

CD4017BMS Key Features

- High Voltage Types (20V Rating)

- Fully Static Operation

- Medium-Speed Operation 10MHz (Typ) at VDD = 10V

- Standardized Symmetrical Output Characteristics

- 100% Tested for Quiescent Current at 20V

- 5V, 10V and 15V Parametric Ratings

- Meets All Requirements of JEDEC Tentative Standard Number 13A, “Standard Specifications for Description of ‘B’ Series CM