CD4022BMS

CD4022BMS is CMOS Counter/Dividers manufactured by Renesas.

- Part of the CD4017BMS comparator family.

- Part of the CD4017BMS comparator family.

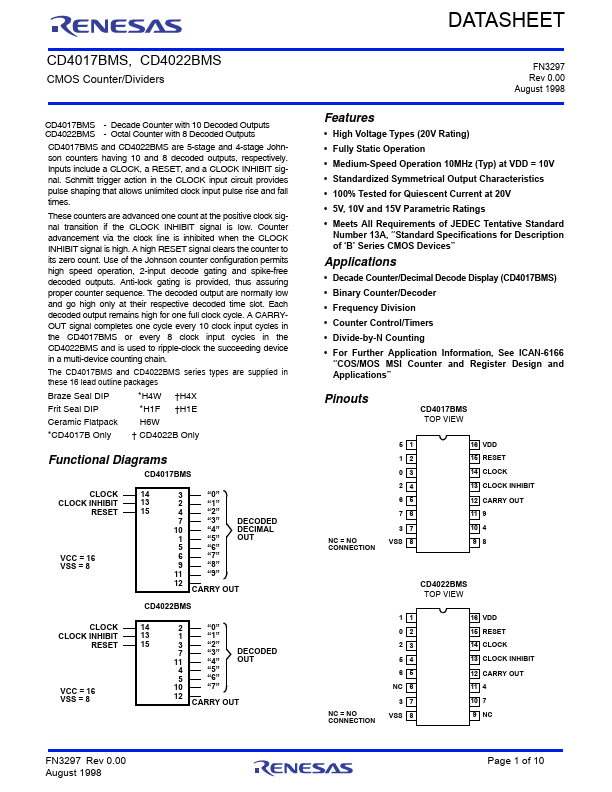

CD4017BMS, CD4022BMS

CMOS Counter/Dividers

CD4017BMS

- Decade Counter with 10 Decoded Outputs CD4022BMS

- Octal Counter with 8 Decoded Outputs

CD4017BMS and CD4022BMS are 5-stage and 4-stage Johnson counters having 10 and 8 decoded outputs, respectively. Inputs include a CLOCK, a RESET, and a CLOCK INHIBIT signal. Schmitt trigger action in the CLOCK input circuit provides pulse shaping that allows unlimited clock input pulse rise and fall times.

These counters are advanced one count at the positive clock signal transition if the CLOCK INHIBIT signal is low. Counter advancement via the clock line is inhibited when the CLOCK INHIBIT signal is high. A high RESET signal clears the counter...