HD74HC573

HD74HC573 is Octal Transparent Latches manufactured by Renesas.

- Part of the HD74HC563 comparator family.

- Part of the HD74HC563 comparator family.

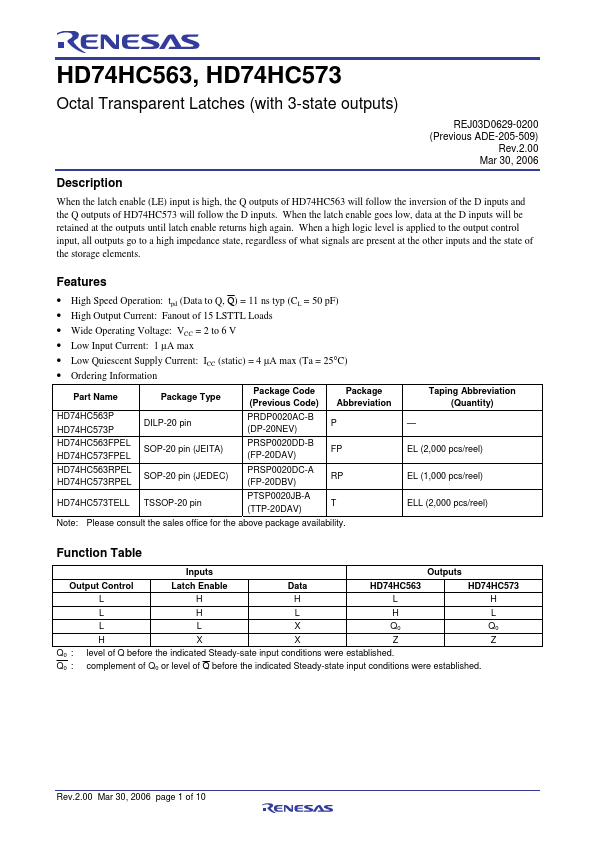

HD74HC563, HD74HC573

Octal Transparent Latches (with 3-state outputs)

REJ03D0629-0200 (Previous ADE-205-509)

Rev.2.00 Mar 30, 2006

Description

When the latch enable (LE) input is high, the Q outputs of HD74HC563 will follow the inversion of the D inputs and the Q outputs of HD74HC573 will follow the D inputs. When the latch enable goes low, data at the D inputs will be retained at the outputs until latch enable returns high again. When a high logic level is applied to the output control input, all outputs go to a high impedance state, regardless of what signals are present at the other inputs and the state of the storage elements.

Features

- High Speed Operation: tpd (Data to Q, Q) =...