| Part | HD74LS148P |

|---|---|

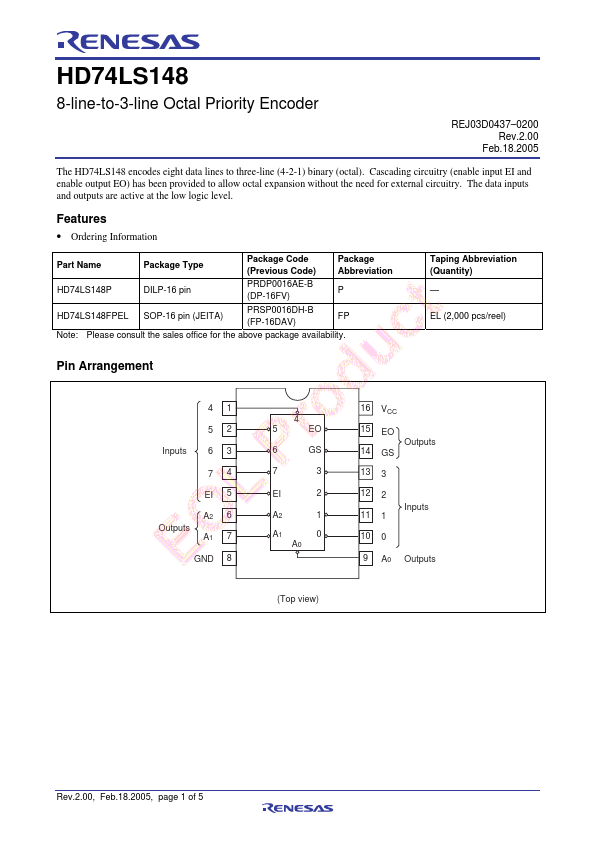

| Description | 8-line-to-3-line Octal Priority Encoder |

| Manufacturer | Renesas |

| Size | 158.69 KB |

Pricing from 2.0619 USD, available from Win Source and SHENGYU ELECTRONICS.

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| Win Source | 200 | 30+ : 2.0619 USD 70+ : 1.6918 USD 110+ : 1.6391 USD 150+ : 1.5862 USD |

View Offer |

| SHENGYU ELECTRONICS | 13152 | 1+ : 0.1838 USD 10+ : 0.1801 USD 100+ : 0.17 USD 1000+ : 0.17 USD |

View Offer |

Similar Parts

| Part Number | Manufacturer | Description |

|---|---|---|

| HD74LS148 | Hitachi Semiconductor | 8-line-to-3-line Octal Priority Encoders |

| HD74LS14 | Hitachi Semiconductor | Hex Schmitt Trigger Inverters |

| HD74LS145 | Hitachi Semiconductor | BCD-to-Decimal Decoders / Drivers |