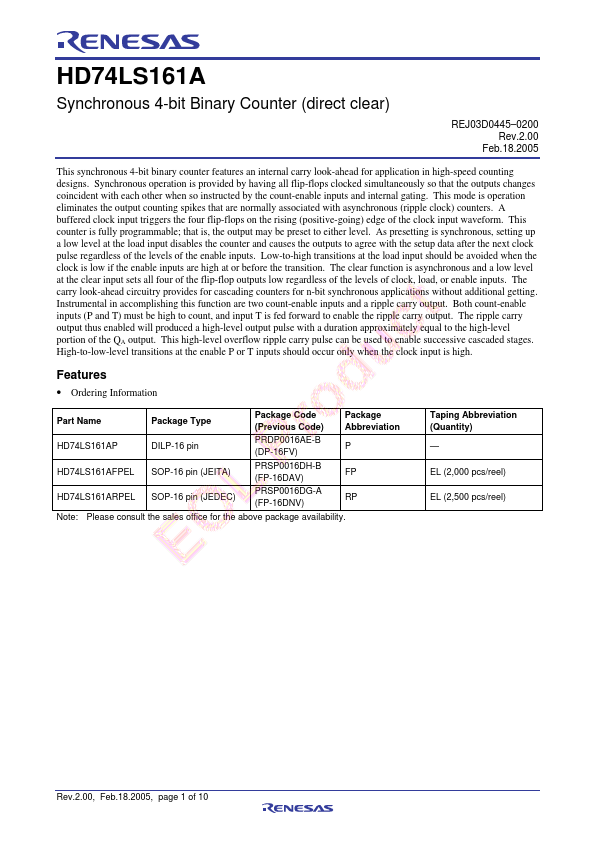

HD74LS161AP Overview

Key Features

- an internal carry look-ahead for application in high-speed counting designs

- This mode is operation eliminates the output counting spikes that are normally associated with asynchronous (ripple clock) counters

- A buffered clock input triggers the four flip-flops on the rising (positive-going) edge of the clock input waveform

- This counter is fully programmable; that is, the output may be preset to either level

- Low-to-high transitions at the load input should be avoided when the clock is low if the enable inputs are high at or before the transition

- The carry look-ahead circuitry provides for cascading counters for n-bit synchronous applications without additional getting

- Instrumental in accomplishing this function are two count-enable inputs and a ripple carry output

- Both count-enable inputs (P and T) must be high to count, and input T is fed forward to enable the ripple carry output

- This high-level overflow ripple carry pulse can be used to enable successive cascaded stages

- High-to-low-level transitions at the enable P or T inputs should occur only when the clock input is high