HD74LS273P

Features

- Ordering Information

Part Name

Package Type

Package Code (Previous Code)

Package Abbreviation

DILP-20 pin

PRDP0020AC-B

(DP-20NEV)

HD74LS273FPEL SOP-20 pin (JEITA)

PRSP0020DD-B

(FP-20DAV)

HD74LS273RPEL SOP-20 pin (JEDEC)

PRSP0020DC-A (FP-20DBV)

Note: Please consult the sales office for the above package availability.

Taping Abbreviation (Quantity)

- EL (2,000 pcs/reel)

EL (1,000 pcs/reel)

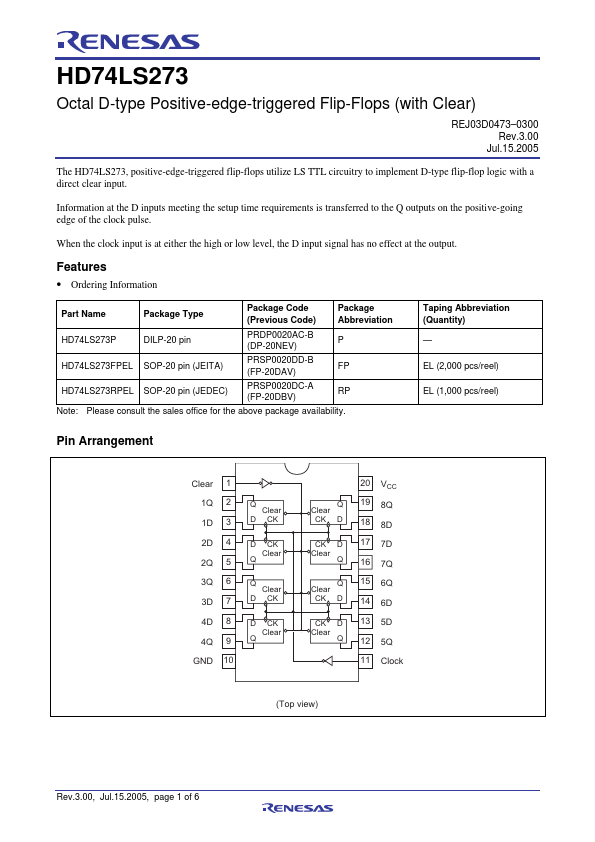

Pin Arrangement

Clear 1 1Q 2 1D 3 2D 4 2Q 5 3Q 6 3D 7 4D 8 4Q 9

GND 10

Q Clear

D CK

D CK Clear

Q Clear

D CK

D CK Clear

Q Clear CK D

CK D Clear

Q Clear CK D

CK D Clear

20 VCC 19 8Q 18 8D 17 7D 16 7Q 15 6Q 14 6D 13 5D 12 5Q 11 Clock

(Top...