| Part | HD74LS74AP |

|---|---|

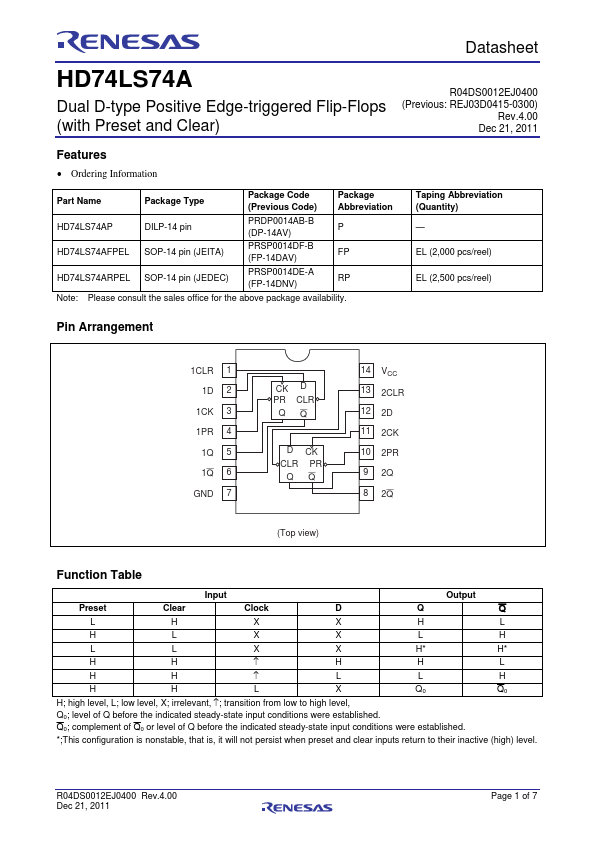

| Description | Dual D-type Positive Edge-triggered Flip-Flops |

| Manufacturer | Renesas |

| Size | 91.37 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| HD74LS74A | Hitachi Semiconductor | Dual D-type Positive Edge-triggered Flip-Flops |

| HD74LS73A | Hitachi Semiconductor | Dual J-K Flip-Flops |

| HD74LS75 | Hitachi Semiconductor | Quadruple Bistable Latches |

| HD74LS76A | Hitachi Semiconductor | Dual J-K Flip-Flop |

| HD74LS77 | Hitachi Semiconductor | 4-bit Bistable Latches |