Datasheet Summary

Preliminary Datasheet

Parallel-Load 8-bit Shift Register

R04DS0002EJ0400 (Previous: REJ03D0321-0300)

Rev.4.00 Aug 16, 2010

Description

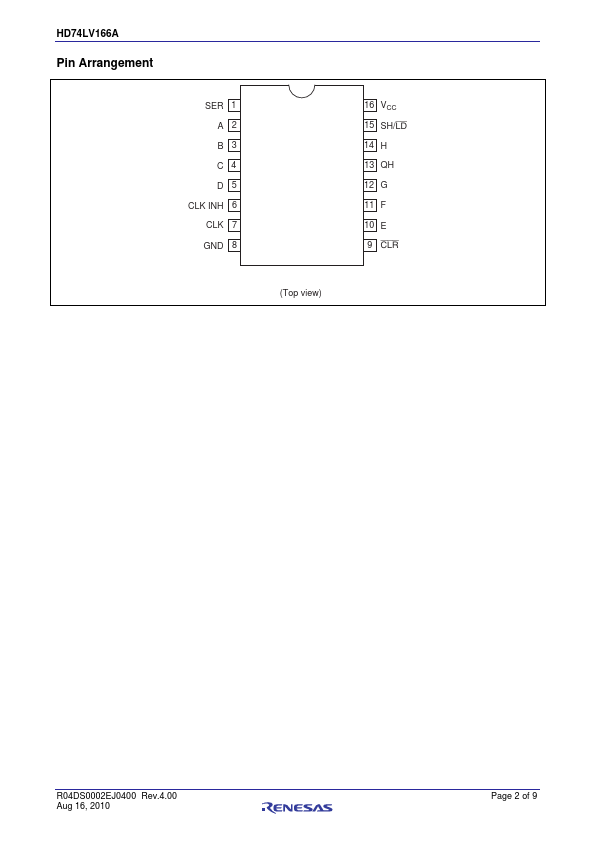

The HD74LV166A is 8-bit shift register with an output from the last stage. Data may be loaded into the register either in parallel or in serial form. When the Shift/Load input is low, the data is loaded asynchronously in parallel. When the Shift/Load input is high, the data is loaded serially on the rising edge of either clock inhibit or Clock. Clear is asynchronous and active-low.

The 2-input NOR clock may be used either by bining two independent clock sources or by designating one of the clock inputs to act as a clock inhibit.

Low-voltage...