ICS180-51

ICS180-51 is LOW EMI CLOCK GENERATOR manufactured by Renesas.

Description

The ICS180-51 generates a low EMI output clock from a clock or crystal input. The device uses IDT’s proprietary mix of analog and digital Phase-Locked Loop (PLL) technology to spread the frequency spectrum of the output, thereby reducing the frequency amplitude peaks by several d B.

The ICS180-51 offers center spread selection of +/-0.625% and +/-1.875%. Refer to the MK1714-01/02 for the widest selection of input frequencies and multipliers.

IDT offers a plete line of EMI reducing clock generators. Consult us when you need to remove crystals and oscillators from your board.

Features

- Pin and function patible to Cypress W180-51

- Packaged in 8-pin SOIC

- Provides a spread spectrum output clock

- Accepts a clock input and provides same frequency dithered output

- Input frequency of 8 to 28 MHz

- Peak reduction by 7d B

- 14d B typical on 3rd

- 19th odd harmonics

- Spread percentage selection for +/-0.625% and

+/-1.875%

- Operating voltage of 3.3 V and 5 V

- Advanced, low-power CMOS process

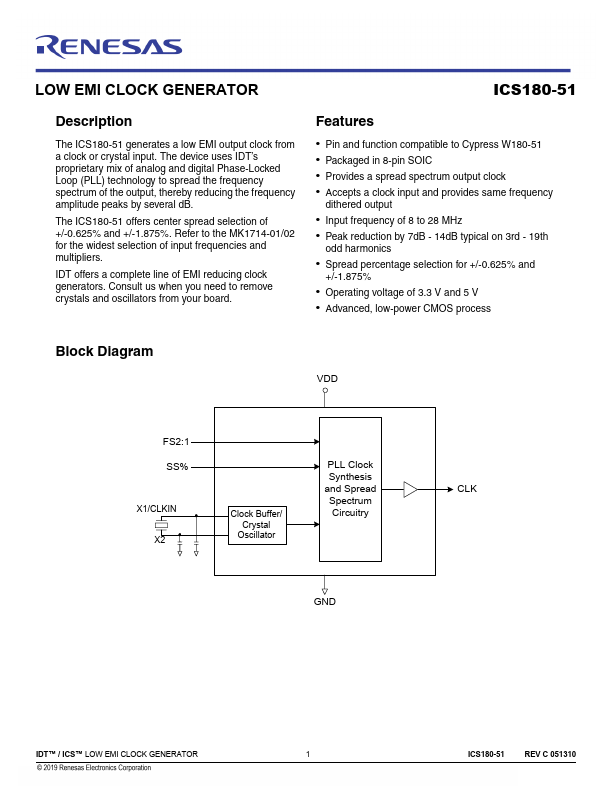

Block Diagram

FS2:1 SS%

X1/CLKIN X2

Clock Buffer/ Crystal

Oscillator

PLL Clock Synthesis and Spread Spectrum Circuitry

IDT™ / ICS™ LOW EMI CLOCK GENERATOR

ICS180-51 REV C 051310

ICS180-51 LOW EMI CLOCK GENERATOR

SSCG

Pin Assignment

Spread Spectrum Select Table

X1/CLKIN 1 X2 2

GND 3 SS% 4

8 FS2 7 FS1 6 VDD 5 CLKOUT

8 pin (150 mil) SOIC

SS% (Pin 4)

0 1

Spread...