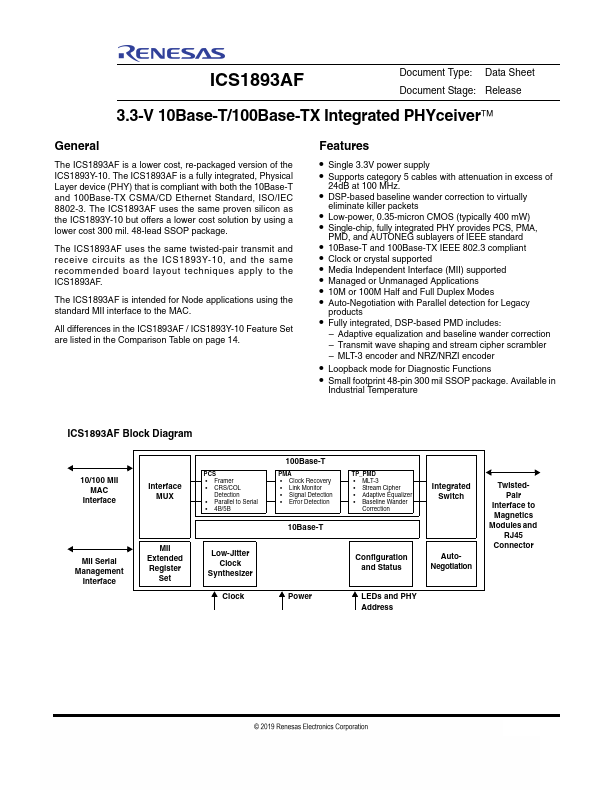

ICS1893AF Overview

Key Specifications

Package: SSOP

Mount Type: Surface Mount

Pins: 48

Operating Voltage: 3.3 V

Key Features

- Single 3.3V power supply

- Supports category 5 cables with attenuation in excess of 24dB at 100 MHz

- DSP-based baseline wander correction to virtually eliminate killer packets

- Low-power, 0.35-micron CMOS (typically 400 mW)

- Single-chip, fully integrated PHY provides PCS, PMA, PMD, and AUTONEG sublayers of IEEE standard