ICS601-01

Description

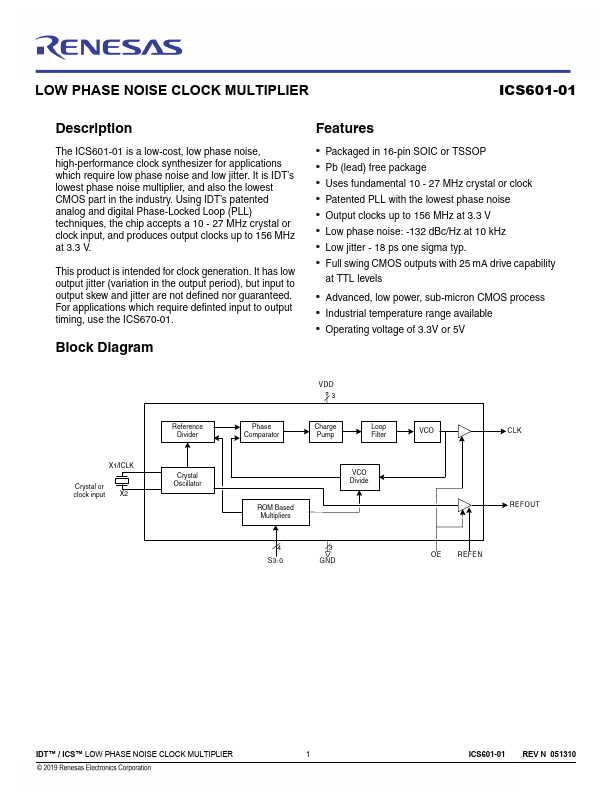

The ICS601-01 is a low-cost, low phase noise, high-performance clock synthesizer for applications which require low phase noise and low jitter.

Key Features

- Packaged in 16-pin SOIC or TSSOP

- Pb (lead) free package

- Uses fundamental 10 - 27 MHz crystal or clock

- Patented PLL with the lowest phase noise

- Output clocks up to 156 MHz at 3.3 V

- Low phase noise: -132 dBc/Hz at 10 kHz

- Low jitter - 18 ps one sigma typ

- Full swing CMOS outputs with 25 mA drive capability at TTL levels

- Advanced, low power, sub-micron CMOS process

- Industrial temperature range available