ICS9250-50 Datasheet Text

Integrated Circuit Systems, Inc.

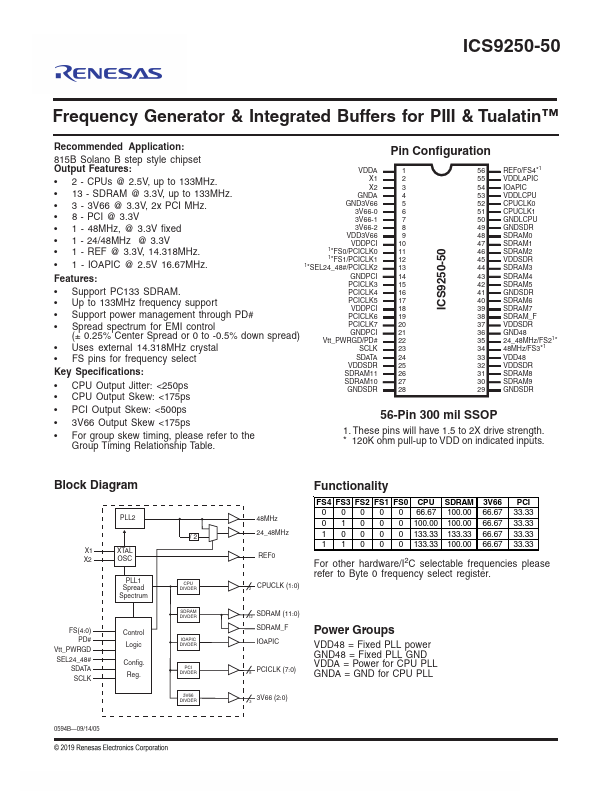

ICS9250-50

Frequency Generator & Integrated Buffers for PIII & Tualatin™

Remended Application:

815B Solano B step style chipset

Output Features

:

VDDA

- 2

- CPUs @ 2.5V, up to 133MHz.

- 13

- SDRAM @ 3.3V, up to 133MHz.

X1 X2 GNDA

- 3

- 3V66 @ 3.3V, 2x PCI MHz.

- 8

- PCI @ 3.3V

GND3V66 3V66-0 3V66-1

- 1

- 48MHz, @ 3.3V fixed

- 1

- 24/48MHz @ 3.3V

- 1

- REF @ 3.3V, 14.318MHz.

- 1

- IOAPIC @ 2.5V 16.67MHz.

3V66-2 VDD3V66

VDDPCI 1- FS0/PCICLK0 1- FS1/PCICLK1 1- SEL24_48#/PCICLK2

Features

:...