IDT2308A

IDT2308A is 3.3V ZERO DELAY CLOCK BUFFER manufactured by Renesas.

IDT2308A 3.3V ZERO DELAY CLOCK MULTIPLIER

MERCIAL AND INDUSTRIAL TEMPERATURE RANGES

3.3V ZERO DELAY CLOCK MULTIPLIER

Features

:

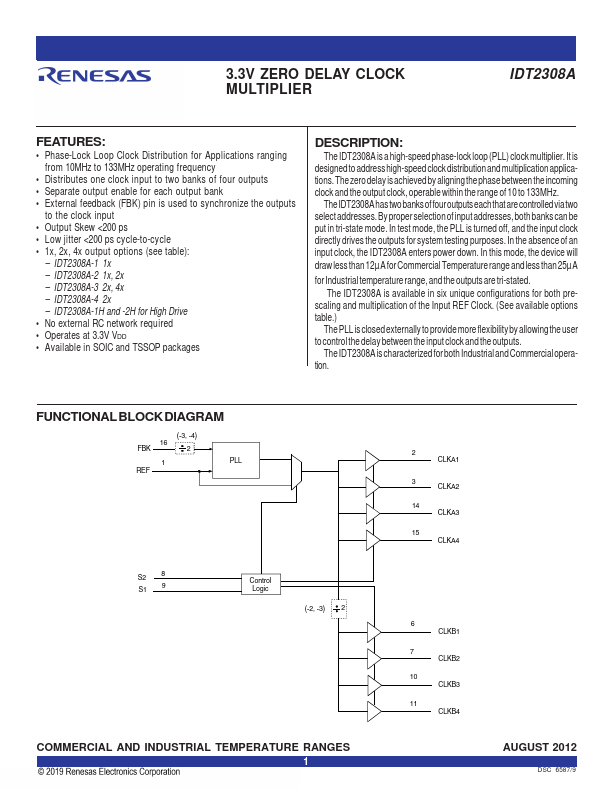

- Phase-Lock Loop Clock Distribution for Applications ranging from 10MHz to 133MHz operating frequency

- Distributes one clock input to two banks of four outputs

- Separate output enable for each output bank

- External feedback (FBK) pin is used to synchronize the outputs to the clock input

- Output Skew <200 ps

- Low jitter <200 ps cycle-to-cycle

- 1x, 2x, 4x output options (see table):

- IDT2308A-1 1x

- IDT2308A-2 1x, 2x

- IDT2308A-3 2x, 4x

- IDT2308A-4 2x

- IDT2308A-1H and -2H for High Drive

- No external RC network required

- Operates at 3.3V...