IDT72V36110 Description

The.

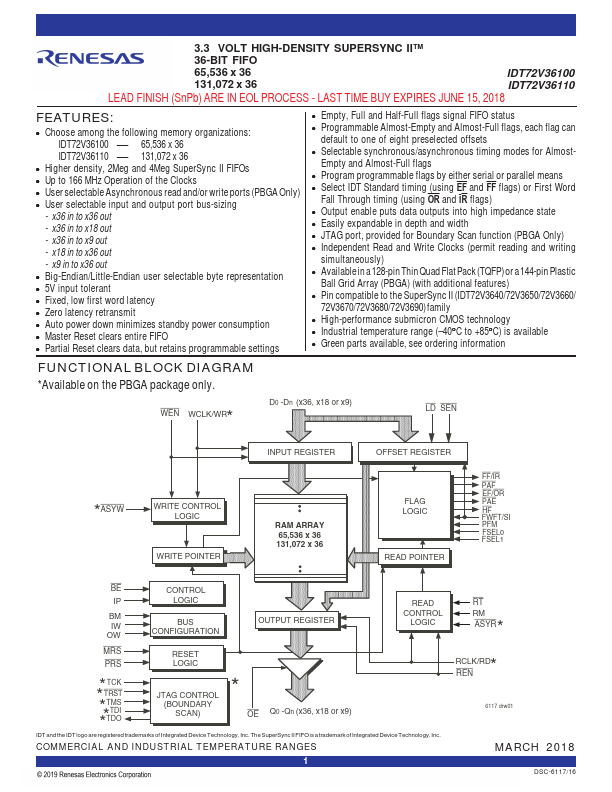

IDT72V36110 Key Features

- Higher density, 2Meg and 4Meg SuperSync II FIFOs

- Up to 166 MHz Operation of the Clocks

- User selectable Asynchronous read and/or write ports (PBGA Only)

- User selectable input and output port bus-sizing

- x36 in to x36 out

- x36 in to x18 out

- x36 in to x9 out

- x18 in to x36 out

- x9 in to x36 out

- Big-Endian/Little-Endian user selectable byte representation