IDT74ALVCH16260 Description

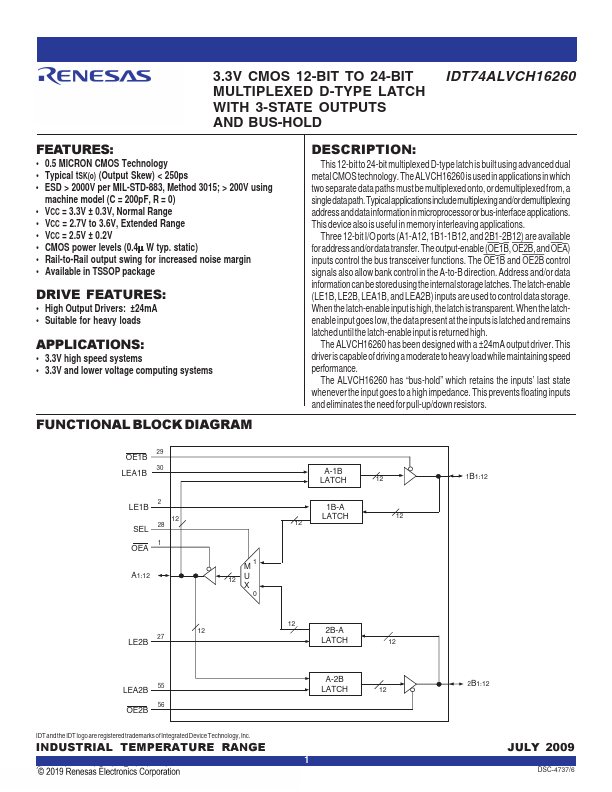

This 12-bit to 24-bit multiplexed D-type latch is built using advanced dual metal CMOS technology. The ALVCH16260 is used in applications in which two separate data paths must be multiplexed onto, or demultiplexed from, a single data path. Typical applications include multiplexing and/or demultiplexing address and data information in microprocessor or bus-interface applications.

IDT74ALVCH16260 Key Features

- 0.5 MICRON CMOS Technology

- Typical tSK(o) (Output Skew) < 250ps

- ESD > 2000V per MIL-STD-883, Method 3015; > 200V using

- VCC = 3.3V ± 0.3V, Normal Range

- VCC = 2.7V to 3.6V, Extended Range

- VCC = 2.5V ± 0.2V

- CMOS power levels (0.4μ W typ. static)

- Rail-to-Rail output swing for increased noise margin

- Available in TSSOP package

- High Output Drivers: ±24mA