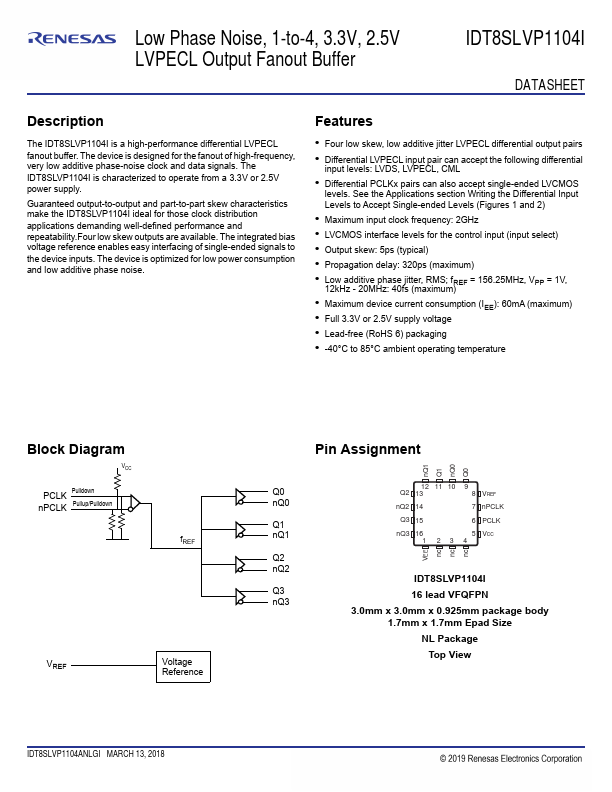

IDT8SLVP1104I Description

The IDT8SLVP1104I is a high-performance differential LVPECL fanout buffer. The device is designed for the fanout of high-frequency, very low additive phase-noise clock and data signals. The IDT8SLVP1104I is characterized to operate from a 3.3V or 2.5V power supply.

IDT8SLVP1104I Key Features

- Four low skew, low additive jitter LVPECL differential output pairs

- Differential LVPECL input pair can accept the following differential

- Differential PCLKx pairs can also accept single-ended LVCMOS