R5F10WLF Overview

Key Specifications

Package: LQFP

Mount Type: Surface Mount

Pins: 64

Operating Voltage: 2 V

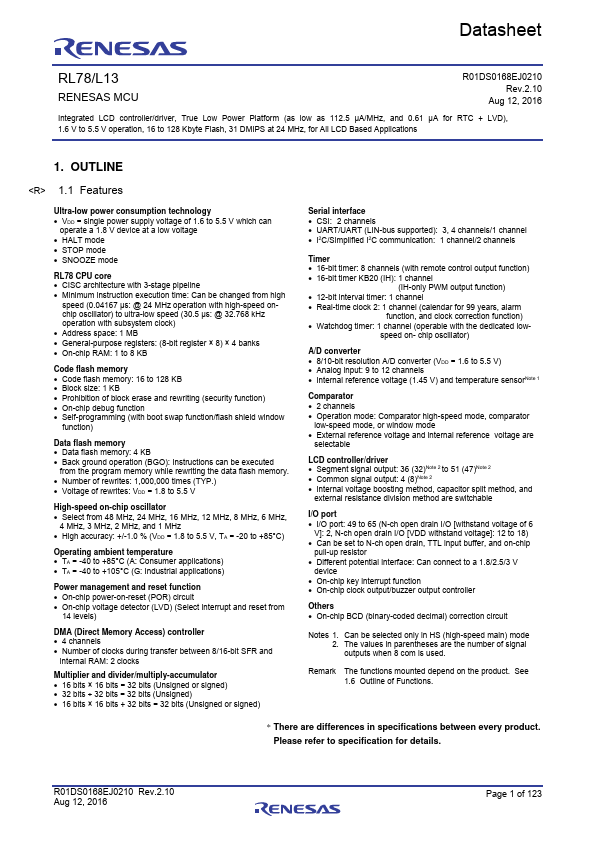

Key Features

- VDD = single power supply voltage of 1.6 to 5.5 V which can operate a 1.8 V device at a low voltage

- SNOOZE mode RL78 CPU core

- CISC architecture with 3-stage pipeline

- Address space: 1 MB

- General-purpose registers: (8-bit register ×