R5F56519FGFP

R5F56519FGFP is 120-MHz 32-bit RX MCU manufactured by Renesas.

- Part of the R5F565NEDDFC comparator family.

- Part of the R5F565NEDDFC comparator family.

Features

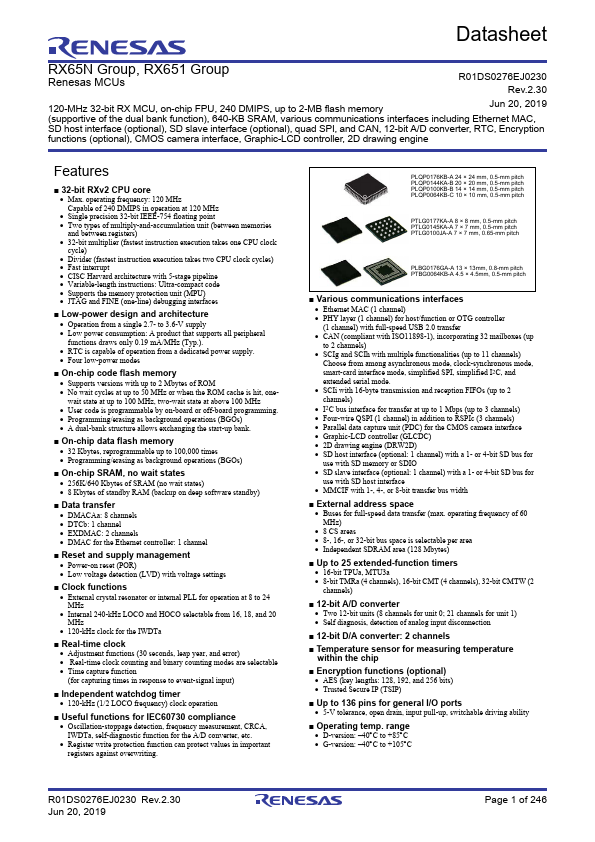

RX65N Group, RX651 Group

Renesas MCUs

R01DS0276EJ0230 Rev.2.30

120-MHz 32-bit RX MCU, on-chip FPU, 240 DMIPS, up to 2-MB flash memory

Jun 20, 2019

(supportive of the dual bank function), 640-KB SRAM, various munications interfaces including Ethernet MAC,

SD host interface (optional), SD slave interface (optional), quad SPI, and CAN, 12-bit A/D converter, RTC, Encryption functions (optional), CMOS camera interface, Graphic-LCD controller, 2D drawing engine

Features

- 32-bit RXv2 CPU core

- Max. operating frequency: 120 MHz Capable of 240 DMIPS in operation at 120 MHz

- Single precision 32-bit IEEE-754 floating point

- Two types of multiply-and-accumulation unit (between memories and between registers)

- 32-bit multiplier (fastest instruction execution takes one CPU clock cycle)

- Divider (fastest instruction execution takes two CPU clock cycles)

- Fast interrupt

- CISC Harvard architecture with 5-stage pipeline

- Variable-length instructions: Ultra-pact code

- Supports the memory protection unit (MPU)

- JTAG and FINE (one-line) debugging interfaces

- Low-power design and architecture

- Operation from a single 2.7- to 3.6-V supply

- Low power consumption: A product that supports all peripheral functions draws only 0.19 m A/MHz (Typ.).

- RTC is capable of operation from a dedicated power supply.

- Four low-power modes

- On-chip code flash memory

- Supports versions with up to 2 Mbytes of ROM

- No wait cycles at up to 50 MHz or when the ROM cache is hit, onewait state at up to 100 MHz, two-wait state at above 100 MHz

- User code is programmable by on-board or off-board programming.

- Programming/erasing as background operations...