M24256-A Description

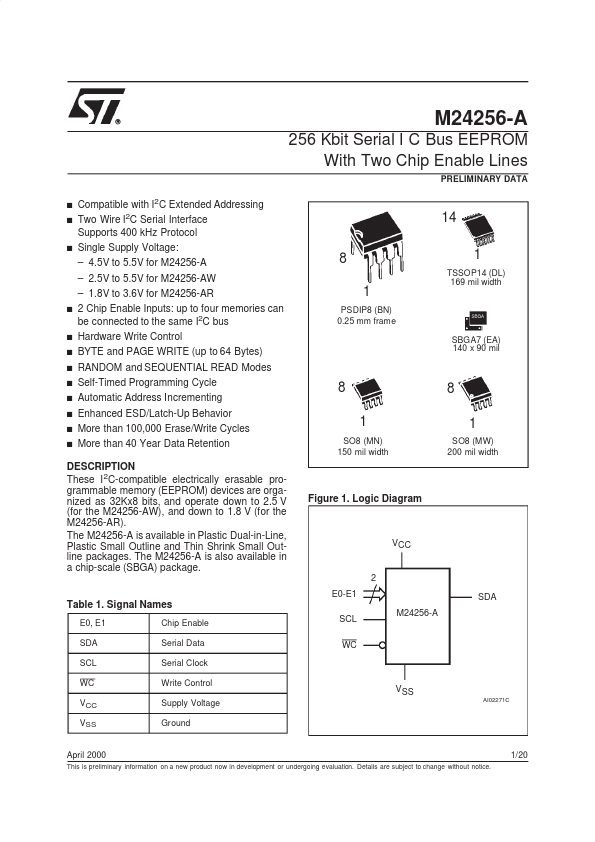

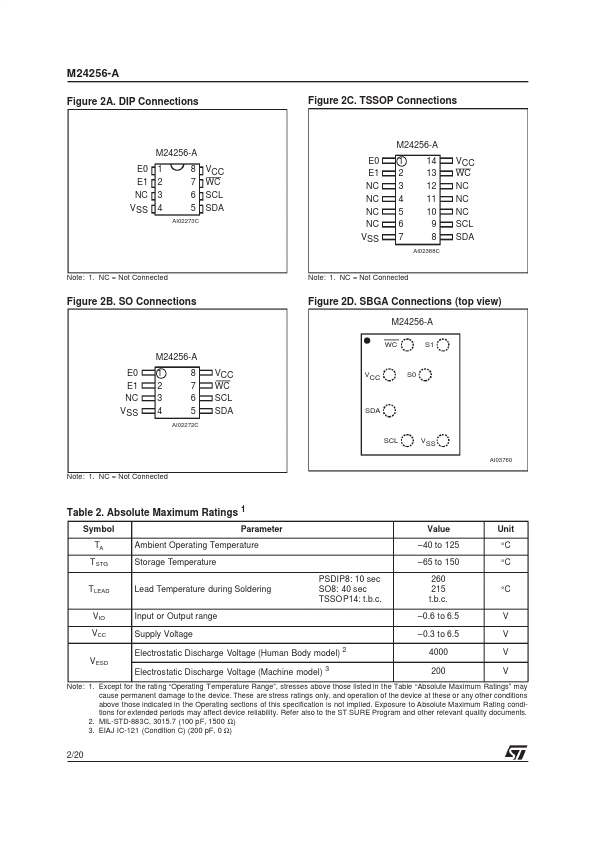

These I 2C-patible electrically erasable programmable memory (EEPROM) devices are organized as 32Kx8 bits, and operate down to 2.5 V (for the M24256-AW), and down to 1.8 V (for the M24256-AR). The M24256-A is available in Plastic Dual-in-Line, Plastic Small Outline and Thin Shrink Small Outline packages. The M24256-A is also available in a chip-scale (SBGA) package.