MC33001B Overview

Description

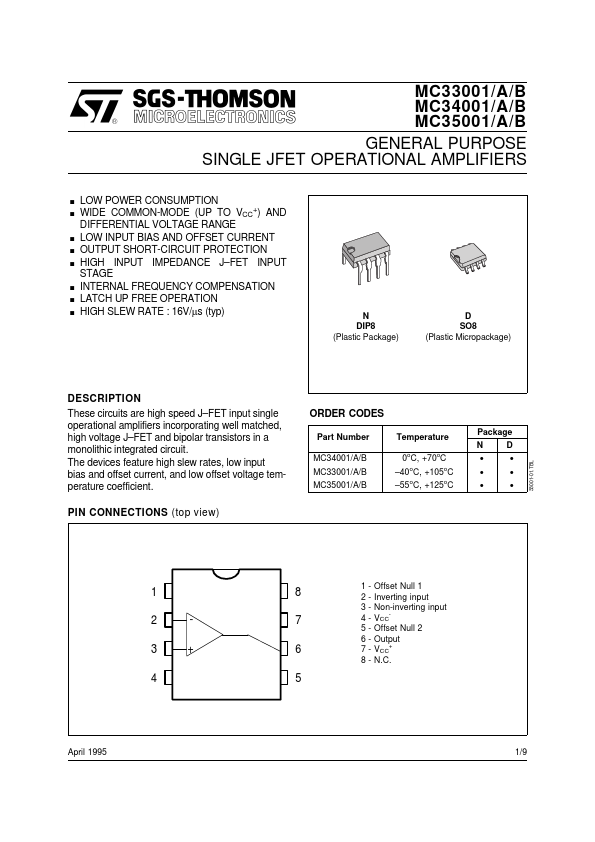

These circuits are high speed J–FET input single operational amplifiers incorporating well matched, high voltage J–FET and bipolar transistors in a monolithic integrated circuit. The devices feature high slew rates, low input bias and offset current, and low offset voltage temperature coefficient.

Key Features

- Offset Null 1 Inverting input Non-inverting input VCCOffset Null 2 Output VCC+ N.C. 5 April 1995 1/9 MC33001/A/B