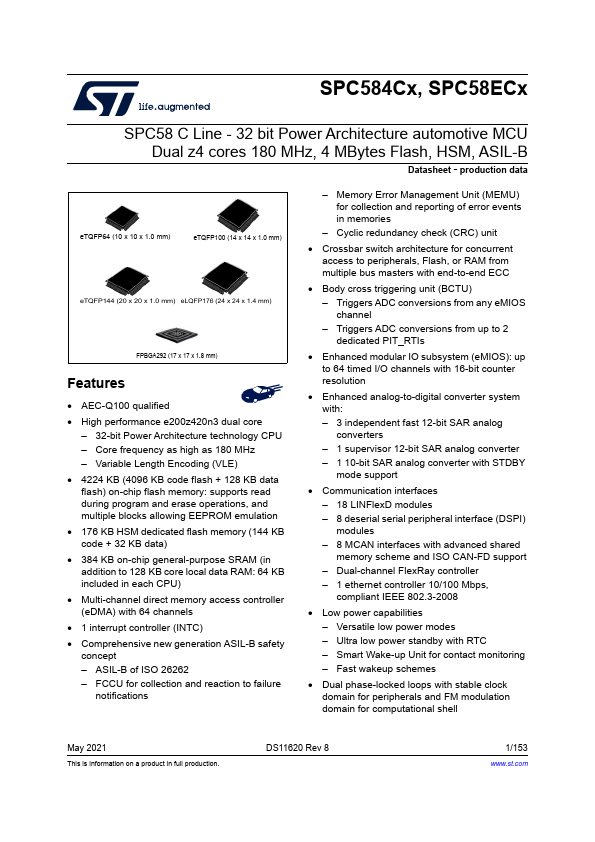

SPC584C74E3 Overview

Key Features

- AEC-Q100 qualified

- 176 KB HSM dedicated flash memory (144 KB code + 32 KB data)

- 384 KB on-chip general-purpose SRAM (in addition to 128 KB core local data RAM: 64 KB included in each CPU)

- Multi-channel direct memory access controller (eDMA) with 64 channels

- 1 interrupt controller (INTC)

- Crossbar switch architecture for concurrent access to peripherals, Flash, or RAM from multiple bus masters with end-to-end ECC

- Enhanced modular IO subsystem (eMIOS): up to 64 timed I/O channels with 16-bit counter resolution