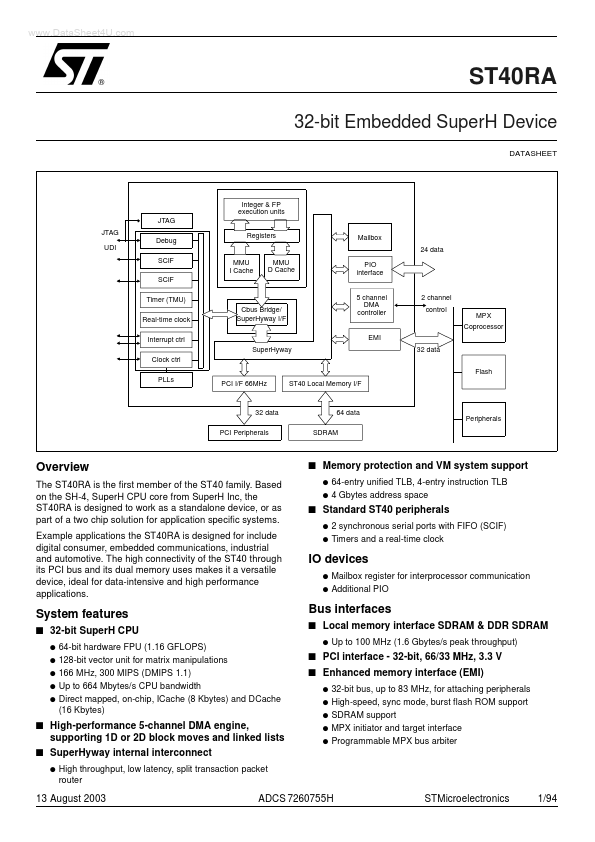

ST40RA Description

Based on the SH-4, SuperH CPU core from SuperH Inc, the ST40RA is designed to work as a standalone device, or as part of a two chip solution for application specific systems. Example applications the ST40RA is designed for include digital consumer, embedded munications, industrial and automotive. The high connectivity of the ST40 through its PCI bus and its dual memory uses makes it a versatile device, ideal for...

ST40RA Key Features

- 32-bit, 66/33 MHz, 3.3 V s Enhanced memory interface (EMI)

- 6 ST40 documentation suite

- 6 System documentation