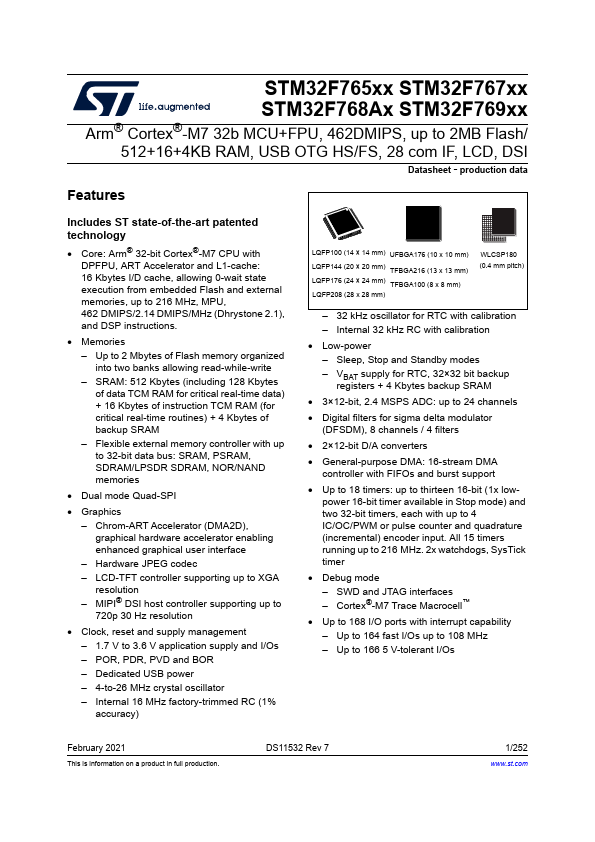

STM32F768

Overview

- Core: Arm® 32-bit Cortex®-M7 CPU with DPFPU, ART Accelerator and L1-cache: 16 Kbytes I/D cache, allowing 0-wait state execution from embedded Flash and external memories, up to 216 MHz, MPU, 462 DMIPS/2.14 DMIPS/MHz (Dhrystone 2.1), and DSP instructions.

- Memories - Up to 2 Mbytes of Flash memory organized into two banks allowing read-while-write - SRAM: 512 Kbytes (including 128 Kbytes of data TCM RAM for critical real-time data) + 16 Kbytes of instruction TCM RAM (for critical real-time routines) + 4 Kbytes of backup SRAM - Flexible external memory controller with up to 32-bit data bus: SRAM, PSRAM, SDRAM/LPSDR SDRAM, NOR/NAND memories

- Dual mode Quad-SPI

- Graphics - Chrom-ART Accelerator (DMA2D), graphical hardware accelerator enabling enhanced graphical user interface - Hardware JPEG codec - LCD-TFT controller supporting up to XGA resolution - MIPI® DSI host controller supporting up to 720p 30 Hz resolution

- Clock, reset and supply management - 1.7 V to 3.6 V application supply and I/Os - POR, PDR, PVD and BOR - Dedicated USB power - 4-to-26 MHz crystal oscillator - Internal 16 MHz factory-trimmed RC (1% accuracy)