STM32H725IE Overview

Key Specifications

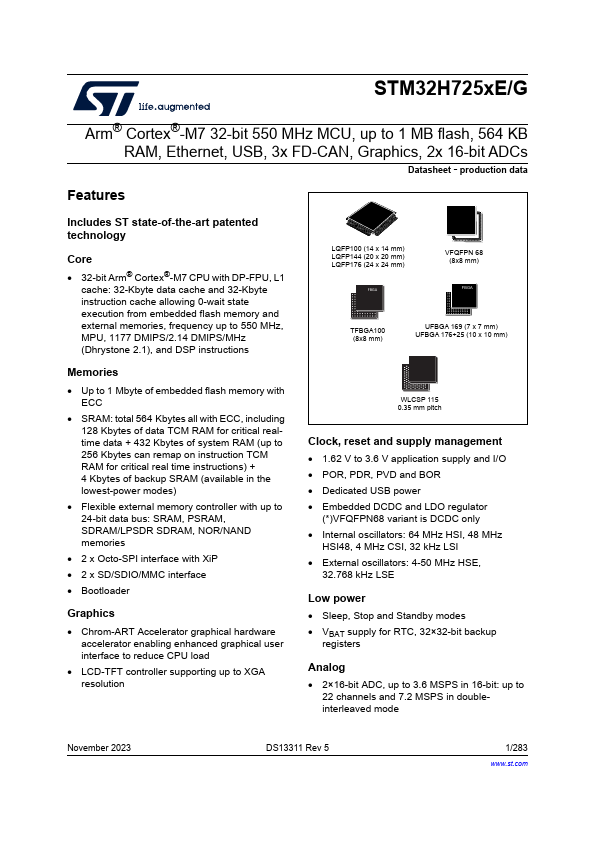

Package: LFQFP

Operating Voltage: 1.8 V

Max Voltage (typical range): 3.6 V

Min Voltage (typical range): 1.62 V

Key Features

- Up to 1 Mbyte of embedded flash memory with ECC

- Flexible external memory controller with up to 24-bit data bus: SRAM, PSRAM, SDRAM/LPSDR SDRAM, NOR/NAND memories

- 2 x Octo-SPI interface with XiP

- 2 x SD/SDIO/MMC interface

- Bootloader Graphics